Dec. 20, 2005

**Sheet 31 of 44**

FIG. 34

Dec. 20, 2005

**Sheet 32 of 44**

FIG. 35

Dec. 20, 2005

**Sheet 33 of 44**

FIG. 36

Dec. 20, 2005

**Sheet 34 of 44**

App. 0697

Dec. 20, 2005

**Sheet 35 of 44**

FIG. 38

Dec. 20, 2005

**Sheet 36 of 44**

FIG. 39

Dec. 20, 2005

**Sheet 37 of 44**

FIG. 40

Dec. 20, 2005

**Sheet 38 of 44**

FIG. 41

Dec. 20, 2005

**Sheet 39 of 44**

FIG. 42

Dec. 20, 2005

**Sheet 40 of 44**

FIG. 43

Dec. 20, 2005

**Sheet 41 of 44**

FIG. 44

Dec. 20, 2005

**Sheet 42 of 44**

FIG. 45A

FIG. 45B

| R | G | R | G |

|---|---|---|---|

| G | В | G | В |

| R | G | R | G |

| Су | Ye |  |

|----|----|--|

| Mg | G  |  |

| Су | Ye |  |

| G  | Mg |  |

Dec. 20, 2005

**Sheet 43 of 44**

FIG. 46

$a_1 > a > a_2$

Dec. 20, 2005

**Sheet 44 of 44**

FIG. 47

1

# ARRANGEMENT OF CIRCUITS IN PIXELS, EACH CIRCUIT SHARED BY A PLURALITY OF PIXELS, IN IMAGE SENSING APPARATUS

# BACKGROUND OF THE INVENTION

The present invention relates to an image sensing apparatus in which a plurality of pixels share a common circuit and an image sensing system using the apparatus.

Conventionally, as an image sensing apparatus using a gain cell, or an active pixel sensor (APS), there are image sensing apparatuses utilizing MOS FET, JFET, bipolar transistor.

These image sensing apparatuses amplify photo-charges 15 generated by photodiodes, that are photoelectric conversion elements, by various methods, then output the amplified photo-charge signals as image information. Since an amplifier for amplifying photo-charge exists in each pixel, the pixel is called a gain cell or an APS.

An APS includes an amplifier and its controller in each pixel, therefore, the percentage of an area reserved for the photoelectric conversion element in a pixel (area ratio) or area where light incidents in a pixel (aperture) tends to be small. This may cause deterioration of the dynamic range, 25 sensitivity, and the S/N ratio of an image sensing apparatus.

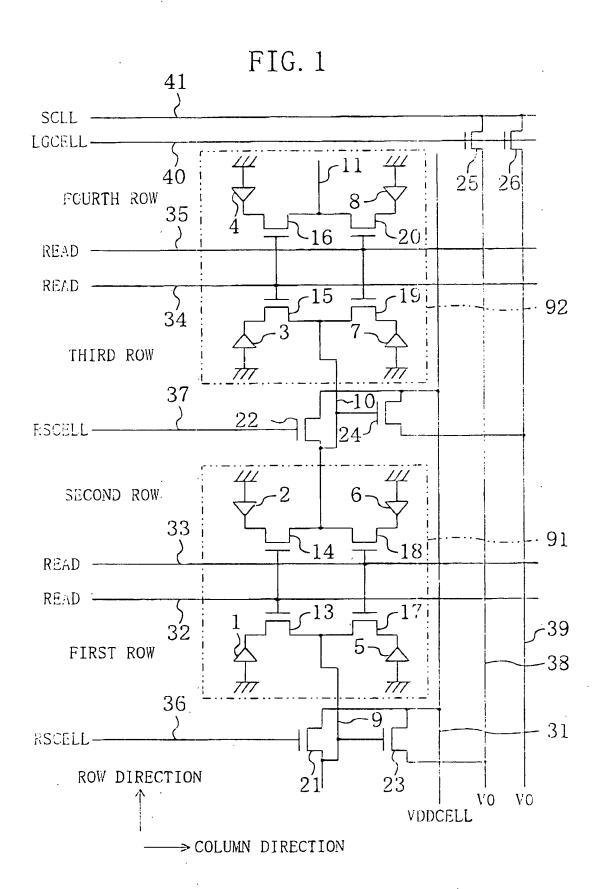

As described above, when an amplifier is provided in each pixel, as shown in FIG. **40**, the aperture decreases. To prevent the decrease in the area or the aperture caused by the amplifier, methods of sharing an amplifier by a plurality of 30 pixels, as disclosed in the Japanese Patent Application Laid-Open Nos. 63-100879 and 9-46596, have been proposed.

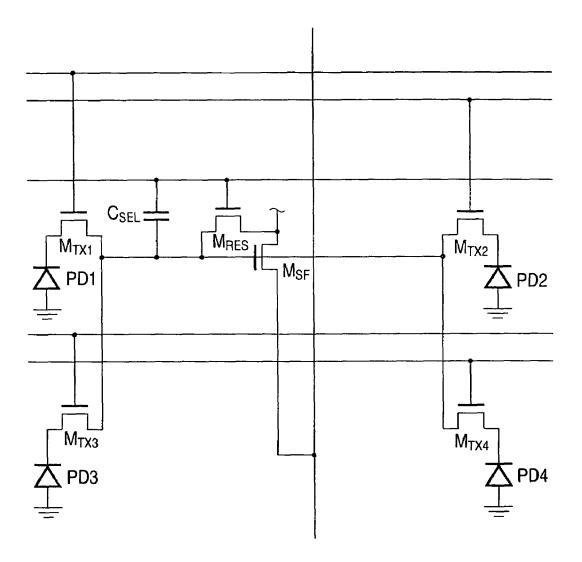

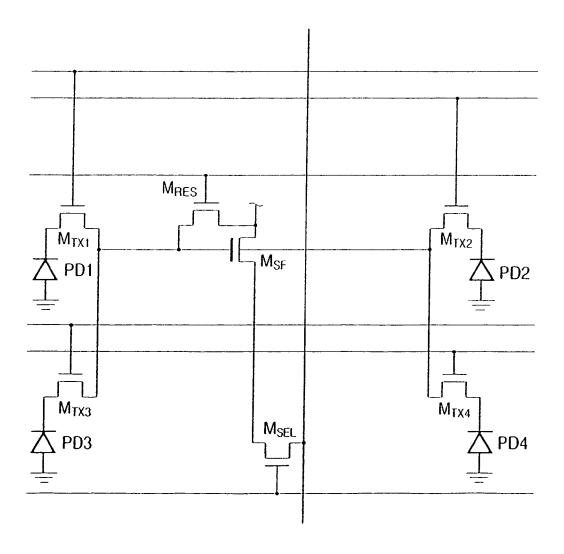

FIGS. 41 and 42 illustrate configurations shown in the above documents. Referring to FIGS. 41 and 42, reference 35 PD1 to PD4 denote photodiodes as photoelectric conversion elements;  $M_{TX1}$  to  $M_{TX4}$  are MOS transistors for transferring photo-charges generated by the photodiodes PD1 to PD4;  $M_{RES}$  is a MOS transistor for resetting the MOS transistors  $M_{TX1}$  to  $M_{TX4}$ ; and  $M_{SF}$  and  $M_{SEL}$  are MOS transistors 40 configuring an amplifier (source follower).  $M_{SEL}$  also functions as a selection switch for selecting a pixel.

However, in the Japanese Patent Application Laid-Open Nos. 63-100879 and 9-46596, no practical layout of the foregoing elements on a chip when a plurality of pixels share 45 a single amplifier is discussed.

Further, there is no description about a layout in a case where an amplifier, shared by a plurality of pixels, is replaced by another unit.

#### SUMMARY OF THE INVENTION

The present invention has been made in consideration of the above situation, and has as its first object to provide an image sensing apparatus, in which a common circuit, such as an amplifier, is shared by a plurality of pixels, achieving good performance without deterioration in resolution.

Further, it is the second object of the present invention to provide an image sensing apparatus having a noise reduction system, preferably used in the image sensing apparatus, in 60 which a common circuit is shared by a plurality of pixels.

It is the third object of the present invention to provide an image sensing system using the foregoing image sensing apparatuses as a sensor unit.

According to the present invention, the foregoing first 65 object is attained by providing an image sensing apparatus having a plurality of unit cells, each including a plurality of

2

photoelectric conversion elements and a common circuit shared by the plurality of photoelectric conversion elements, arranged in either one or two dimensions, wherein the plurality of photoelectric conversion elements are arranged at a predetermined interval.

The first object is also attained by providing an image sensing apparatus having a plurality of unit cells, each including a plurality of photoelectric conversion elements and a common circuit shared by the plurality of photoelectric conversion elements, arranged in two dimensions, wherein photoelectric conversion elements, out of the plurality of photoelectric conversion elements, which are covered by a color filter that contributes mostly to forming a luminance signal are arranged in a same interval both in the horizontal and vertical directions by arranging adjoining rows or columns of photoelectric conversion elements shifted from each other.

Further, the first object is also attained by providing an image sensing apparatus having a plurality of unit cells, each including a plurality of photoelectric conversion elements and a common circuit shared by the plurality of photoelectric conversion elements, arranged in either one or two dimensions, characterized by comprising adjustment means for adjusting centers of mass of light-receiving areas of the plurality of photoelectric conversion elements provided in a central portion of the image sensing apparatus, so as to be apart at a same spatial interval.

Furthermore, the first object is also attained by providing an image sensing apparatus having a plurality of unit cells, each including a plurality of photoelectric conversion elements and a common circuit shared by the plurality of photoelectric conversion elements, arranged in either one or two dimensions, characterized by comprising adjustment means for adjusting centers of mass of light-receiving areas of photoelectric conversion elements selected from the plurality of photoelectric conversion elements, provided in a central portion of the image sensing apparatus, on the basis of a predetermined condition, so as to be apart at a same spatial interval.

Further, to achieve the second object of the present invention, noise reading means for reading a noise of the common circuit; first signal reading means for reading a first signal through the common circuit; second signal reading means for reading a second signal through the common circuit; and noise reduction means for reducing the noise from the first and second signals are further provided.

Alternatively, noise reading means for reading a noise of the common circuit; signal reading means for reading a plurality of signals through the common circuit; and noise for reduction means for reducing the noise from the plurality of signals are further provided.

Further, the third object of the present invention is achieved by providing an image sensing system having the image sensing apparatus as described above, a lens system for forming an image on the image sensing apparatus, and a signal processing circuit for processing an output signal from the image sensing apparatus.

Other features and advantages of the present invention will be apparent from the following description taken in conjunction with the accompanying drawings, in which like reference characters designate the same or similar parts throughout the FIG. 5res thereof.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The accompanying drawings, which are incorporated in and constitute a part of the specification, illustrate embodi-

3

ments of the invention and, together with the description, serve to explain the principles of the invention.

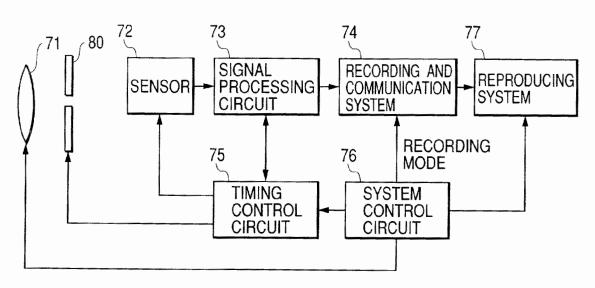

- FIG. 1 is a block diagram illustrating a configuration of the image sensing system according to an embodiment of the present invention;

- FIG. 2A shows a layout of amplifiers in pixels according to a first embodiment of the present invention;

- FIG. 2B shows another layout of amplifiers in pixels according to the first embodiment of the present invention;

- FIG. 3 shows a practical pattern layout of two photo- <sup>10</sup> diodes and an amplifier according to the first embodiment of the present invention;

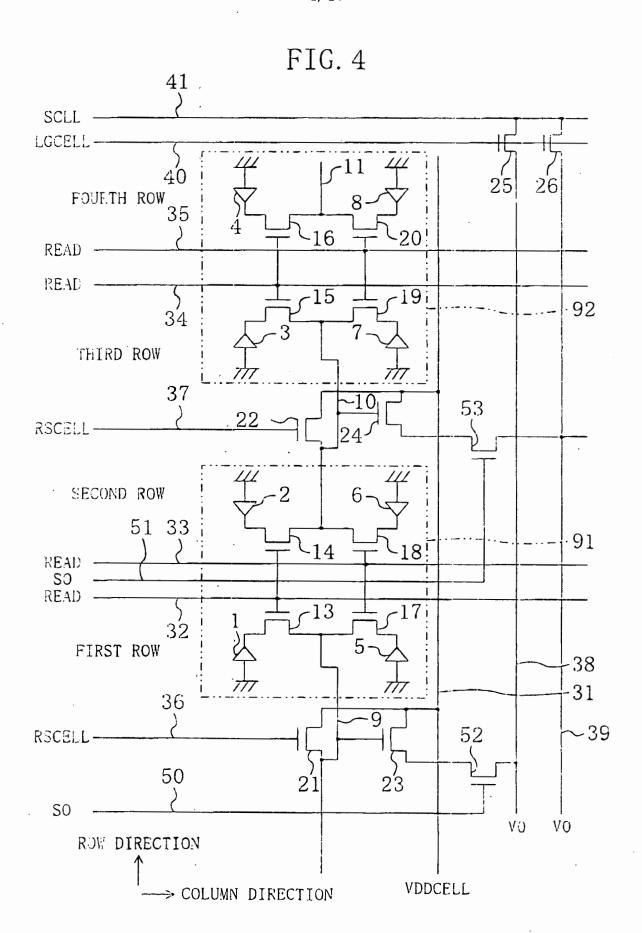

- FIG. 4 is a brief view of FIG. 3 from which a part of lines are omitted;

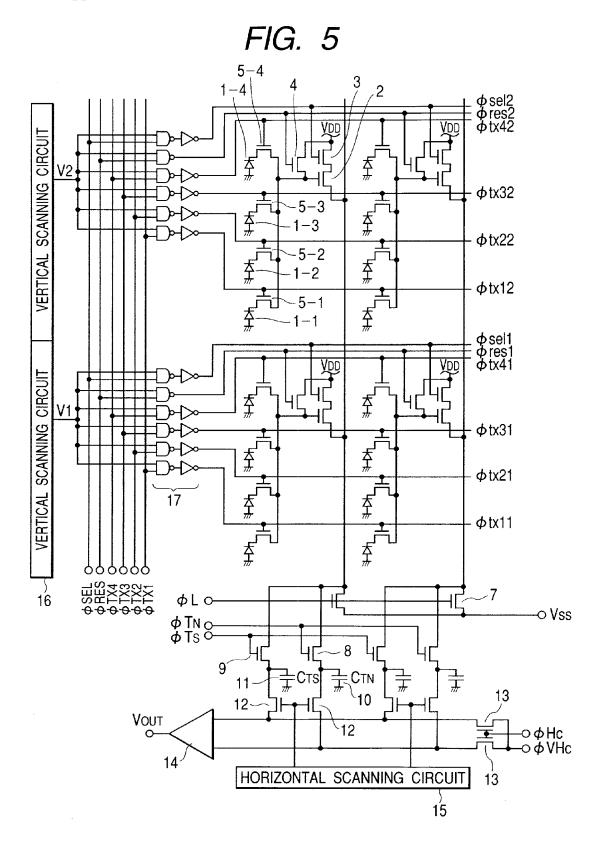

- FIG. 5 shows another practical pattern layout of two <sup>15</sup> photodiodes and an amplifier according to the first embodiment of the present invention;

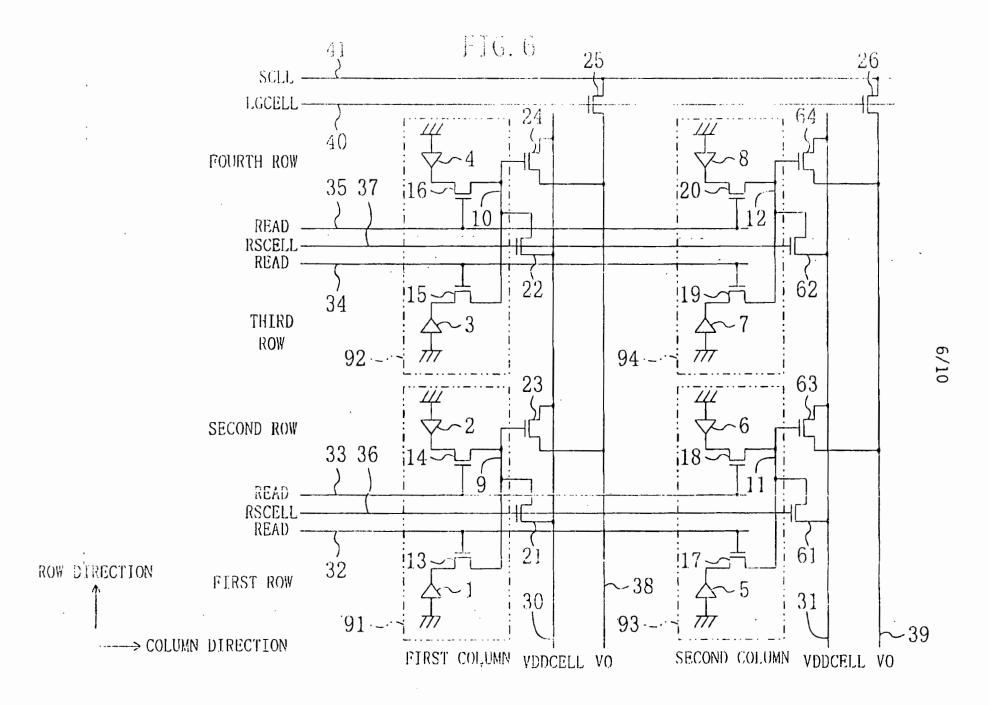

- FIG. 6 is a brief view of FIG. 5 from which a part of lines are omitted;

- FIG. 7 is an enlarged view showing vicinity of a floating diffusion portion according to the first embodiment of the present invention;

- FIG. 8 is an enlarged view showing vicinity of the floating diffusion portion according to the first embodiment of the present invention;

- FIG. 9 is a circuit diagram of a unit cell of a CMOS sensor in which two photodiodes share one amplifier according to the first embodiment of the present invention;

- FIG. 10 is a circuit diagram of the image sensing apparatus including a signal processing circuit according to the first embodiment of the present invention;

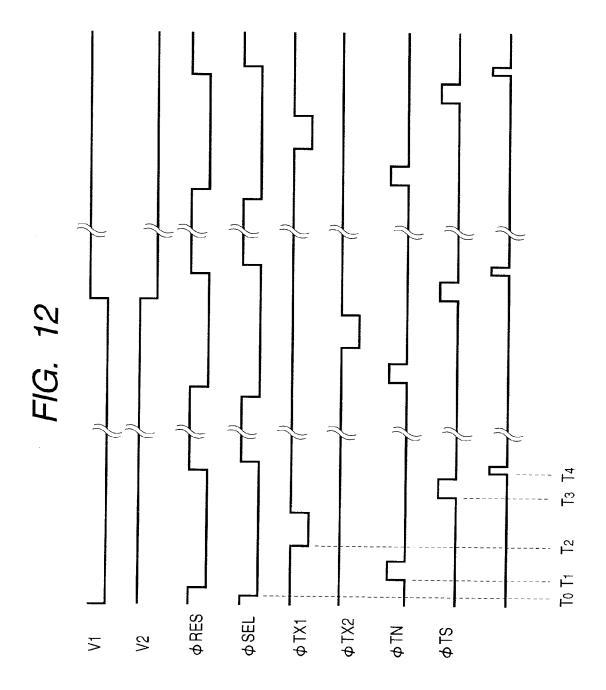

- FIG. 11 is a timing chart for operating an image sensing apparatus according to the first and second embodiments of the present invention;

- FIG. 12 is a timing chart for operating the apparatus according to the first and second embodiments of the present invention:

- FIG. 13 shows a layout of common circuits in pixels according to the second embodiment of the present invention;

- FIG. 14 shows another layout of common circuits in pixels according to the second embodiment of the present invention:

- FIG. 15 is a practical pattern layout of the common <sup>45</sup> circuits each shared by two photodiodes according to the second embodiment of the present invention;

- FIG. 16 is a circuit diagram of the image sensing apparatus including a signal processing circuit according to the second embodiment of the present invention;

- FIG. 17 is a circuit diagram of a unit cell configured with a common circuit and photodiodes according to the second embodiment of the present invention;

- FIG. 18 is an explanatory view for explaining a signal processing circuit;

- FIG. 19 is a layout of amplifiers in pixels according to a third embodiment of the present invention;

- FIG. 20 is another layout of amplifiers in pixels according to the third embodiment of the present invention;

- FIG. 21 is another layout of amplifiers in pixels according to the third embodiment of the present invention;

- FIG. 22 is another layout of amplifiers in pixels according to the third embodiment of the present invention;

- FIG. 23 is a practical pattern layout of four photodiodes 65 and an amplifier according to the third embodiment of the present invention;

4

- FIG. 24 is another practical pattern layout of four photodiodes and an amplifier according to the third embodiment of the present invention;

- FIG. 25 is an explanatory view for explaining a variation of a layout;

- FIG. 26 shows a practical pattern layout according to the third embodiment of the present invention;

- FIG. 27 shows another layout of light-receiving areas according to the third embodiment of the present invention;

- FIG. 28 shows another practical pattern layout of four photodiodes and an amplifier according to the third embodiment of the present invention;

- FIG. 29 is an example when on-chip lens according to the third embodiment of the present invention;

- FIG. 30 is a circuit diagram of a unit cell of a CMOS sensor having the aforesaid configurations according to the third embodiment of the present invention;

- FIG. 31 is a circuit diagram of the image sensing apparatus including a signal processing unit according to the third embodiment of the present invention;

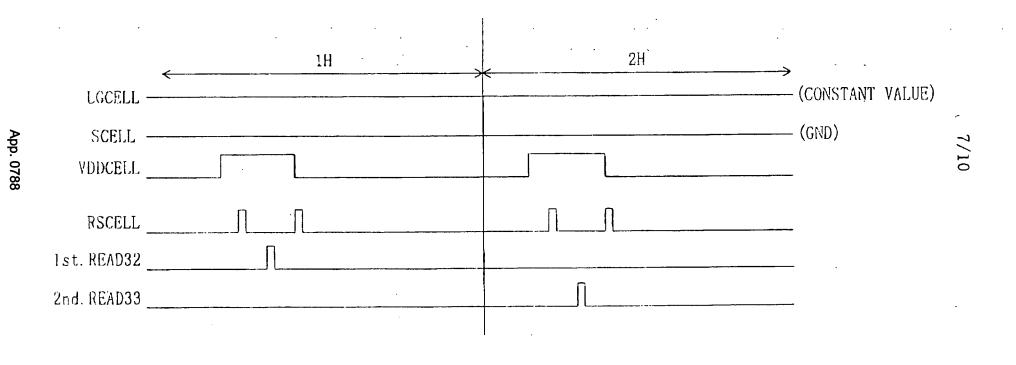

- FIG. 32 is a timing chart for operating an image sensing apparatus according to the third embodiment of the present invention;

- FIG. 33 is a circuit diagram of an image sensing apparatus including the signal processing unit according to a first modification of the third embodiment of the present invention:

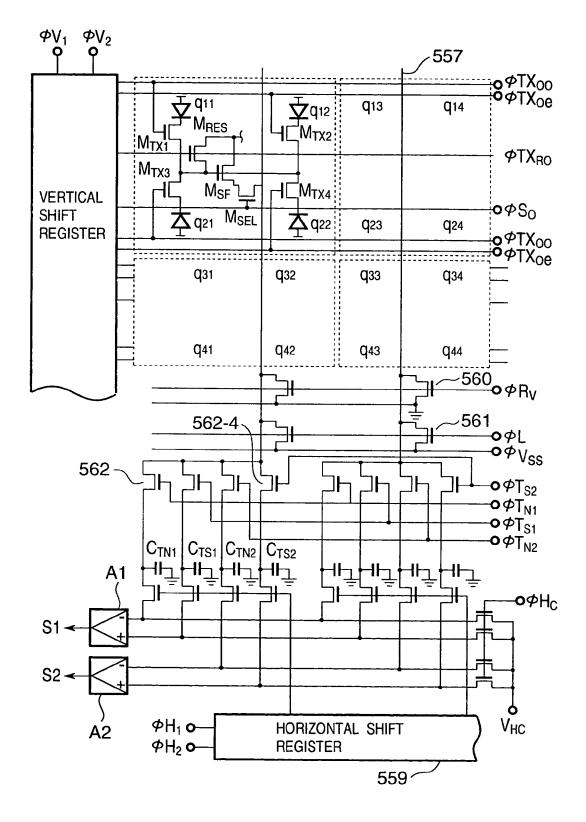

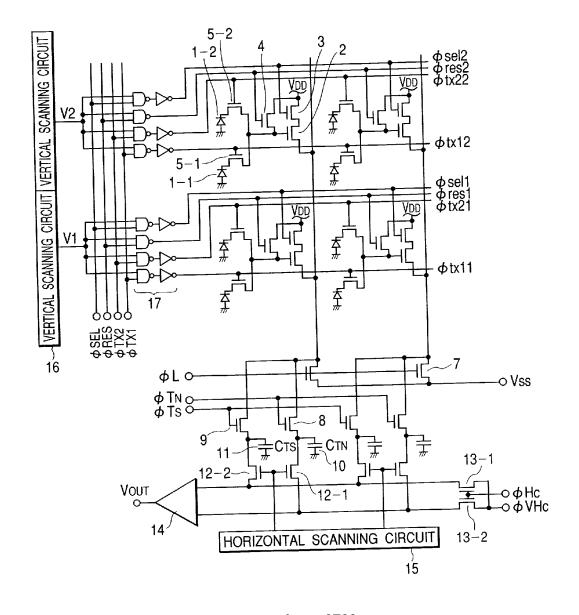

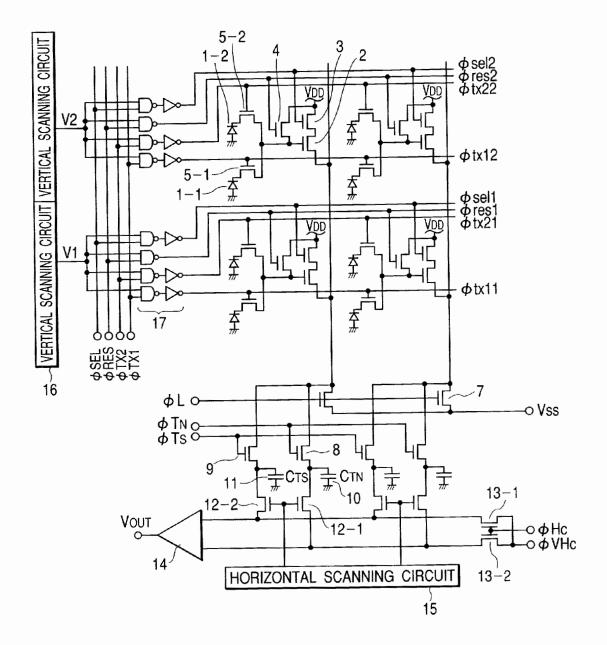

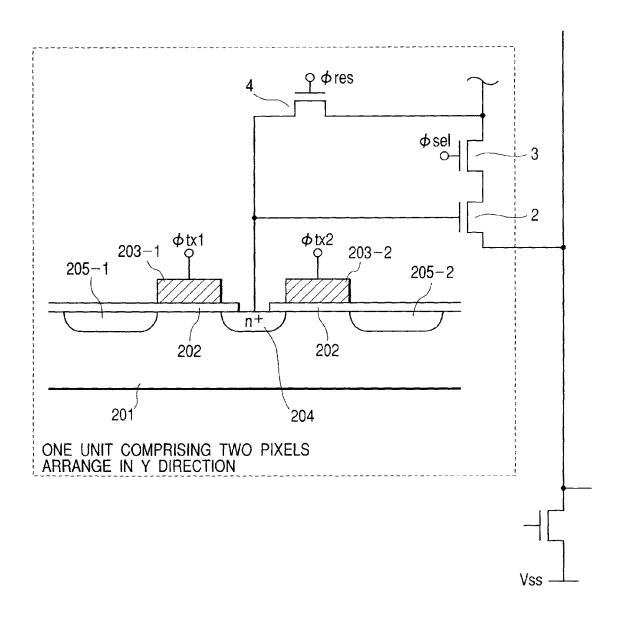

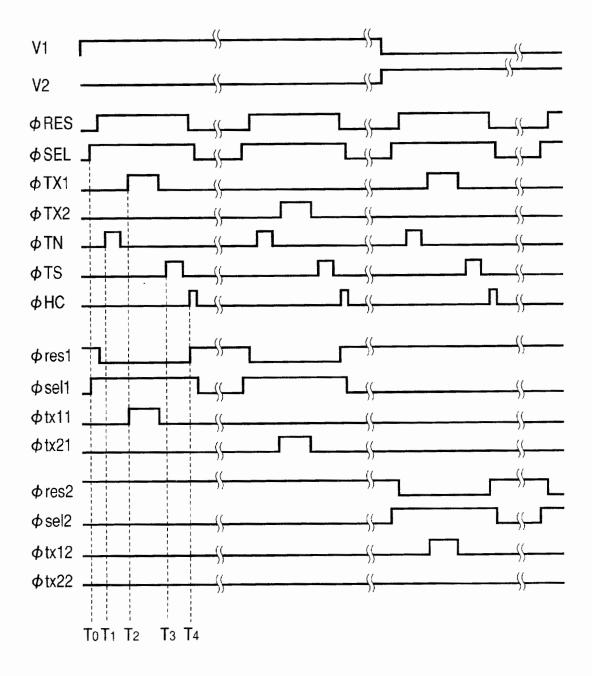

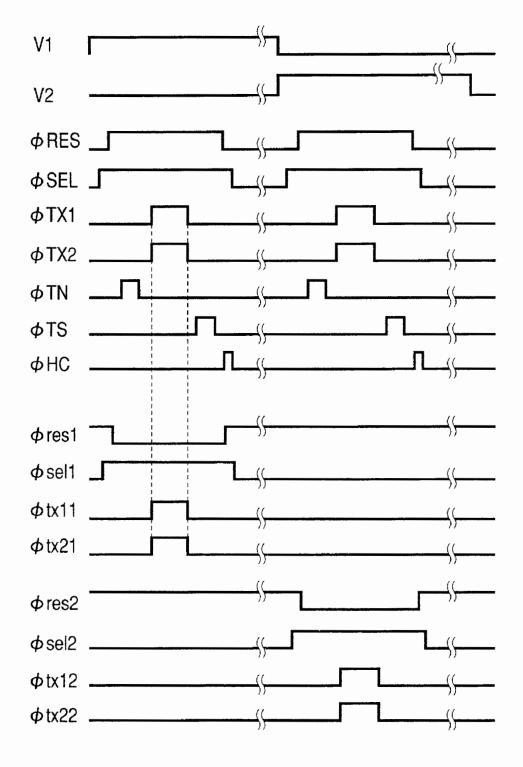

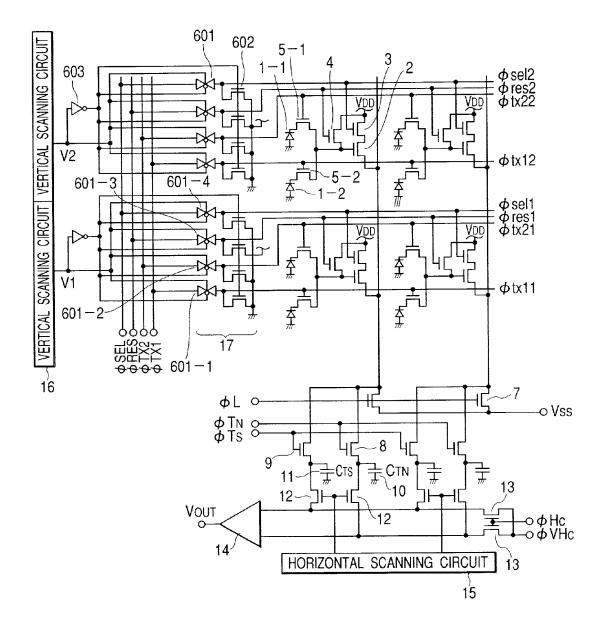

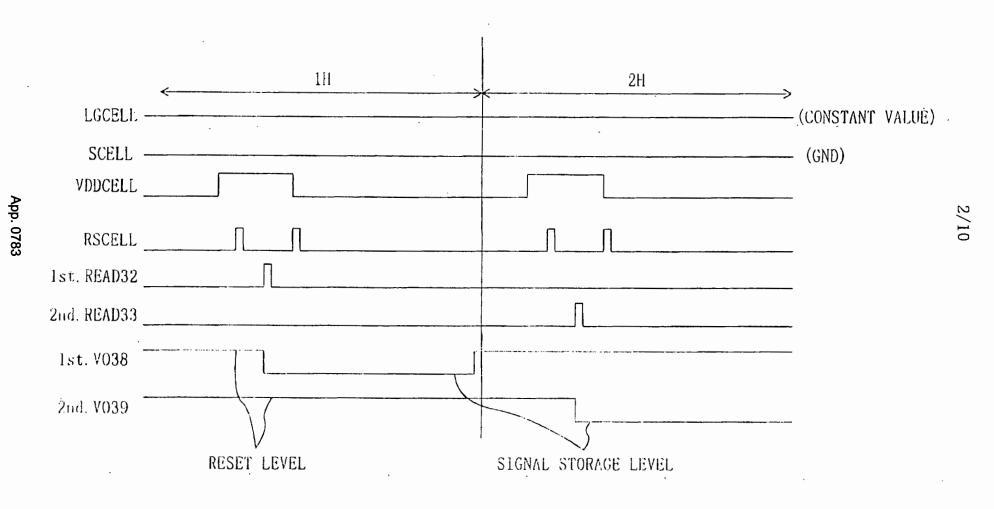

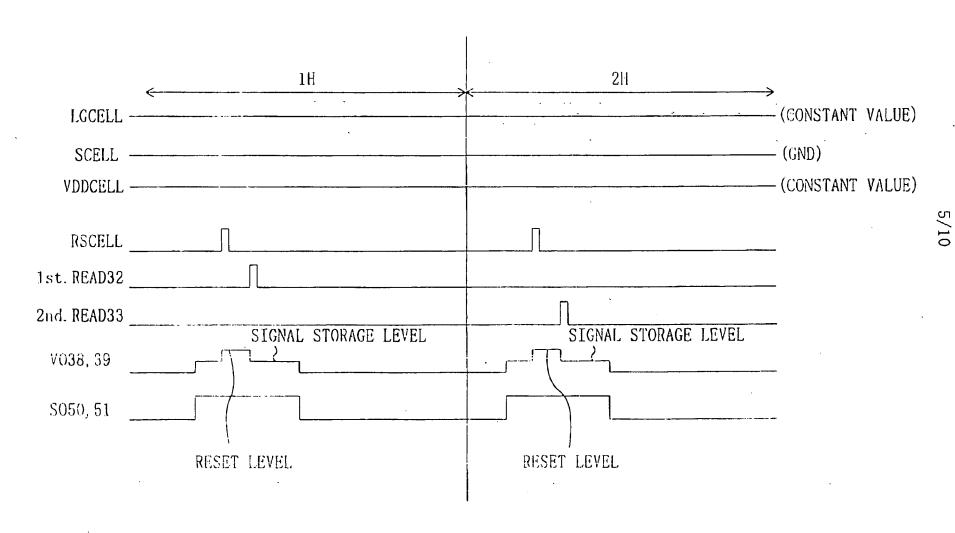

- FIG. 34 is a circuit diagram of an image sensing apparatus including a signal processing unit according to a second modification of the third embodiment of the present invention;

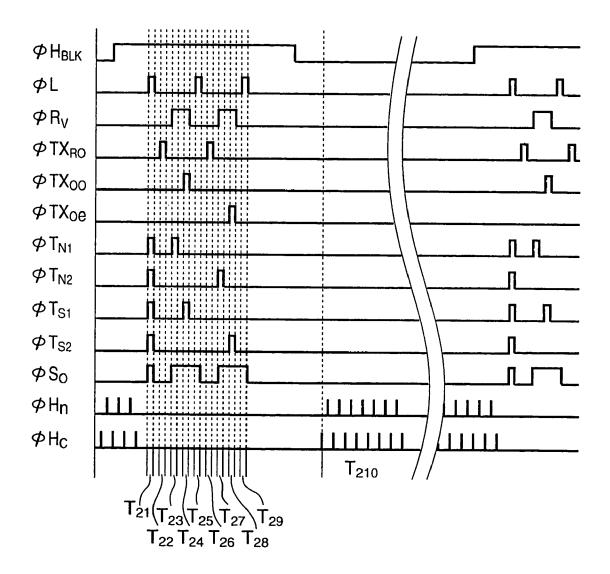

- FIG. 35 is a timing chart for operating the image sensing apparatus shown in FIG. 34 according to the second modification of the third embodiment of the present invention;

- FIG. 36 is a timing chart during a vertical blanking period according to the second configuration of the third embodiment of the present invention;

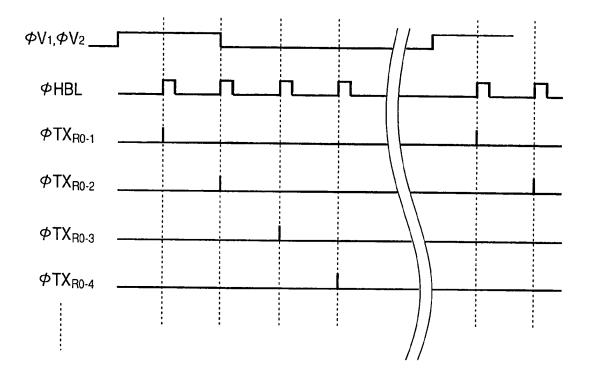

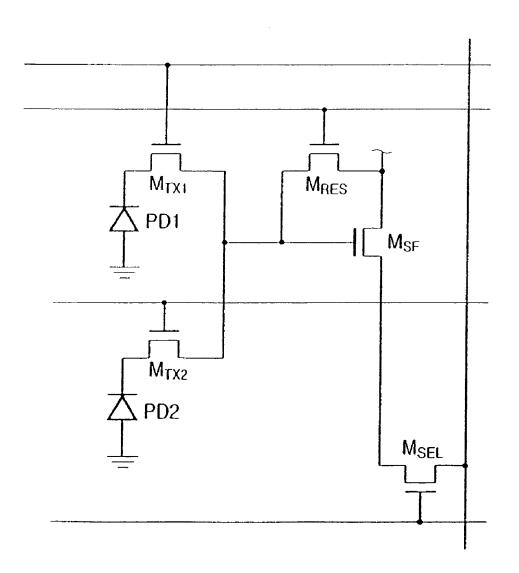

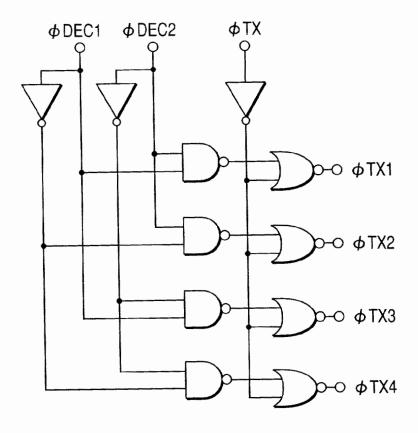

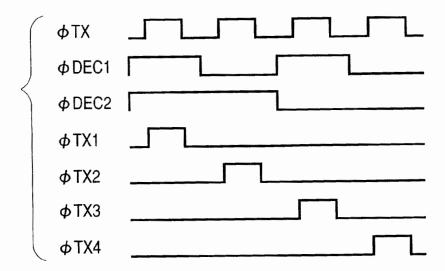

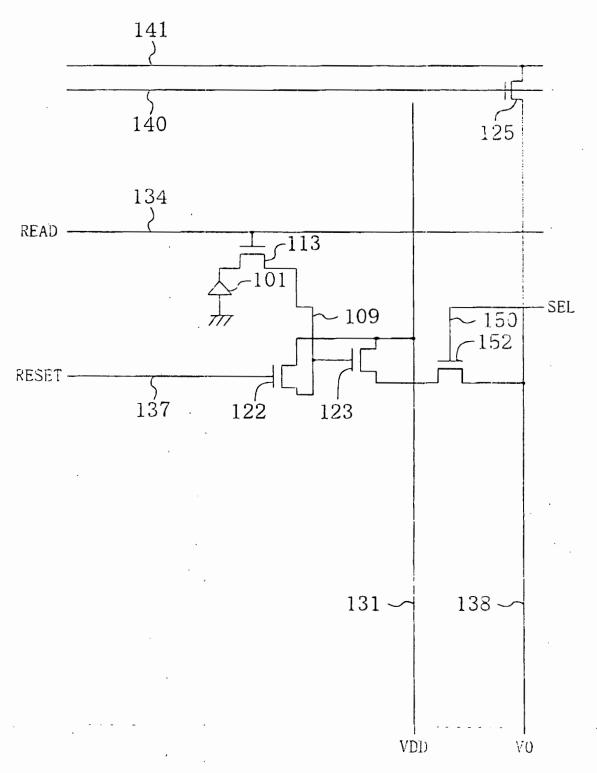

- FIG. 37 shows a configuration of a common circuit according to a fourth embodiment of the present invention;

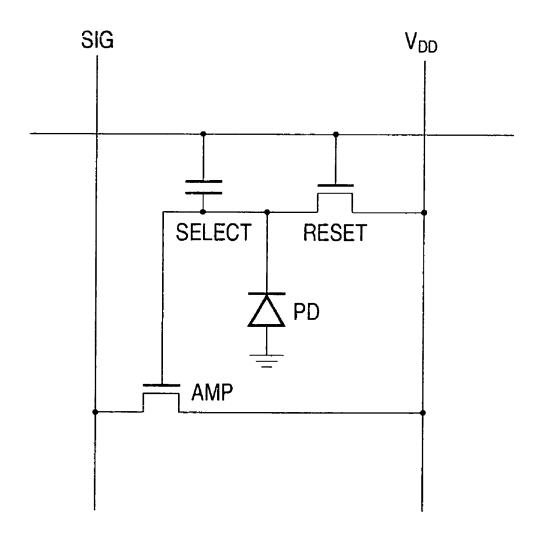

- FIG. 38 is a circuit diagram of a unit cell of another image sensor to which the present invention is applied;

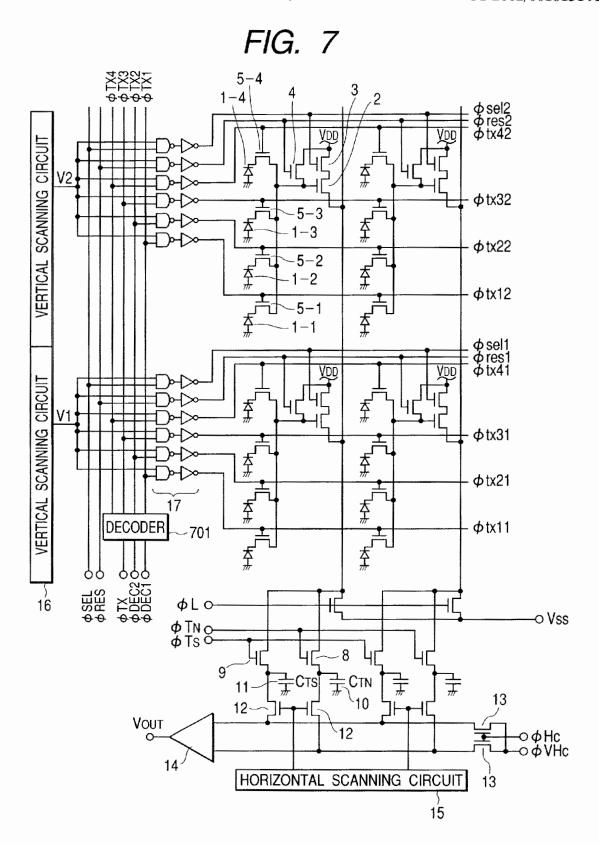

- FIG. 39 is a circuit diagram of a configuration of an amplifier shared by four photodiodes according to an embodiment of the present invention;

- FIG. 40 shows a conventional layout of amplifiers in pixels;

- FIG. 41 is a circuit diagram of a conventional configuration;

- FIG. 42 is a circuit diagram of another conventional configuration;

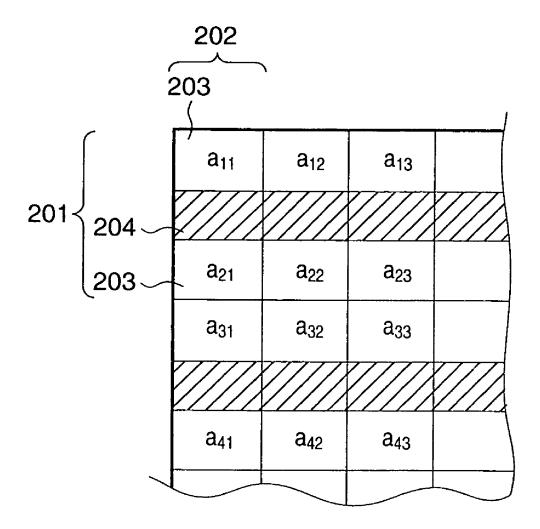

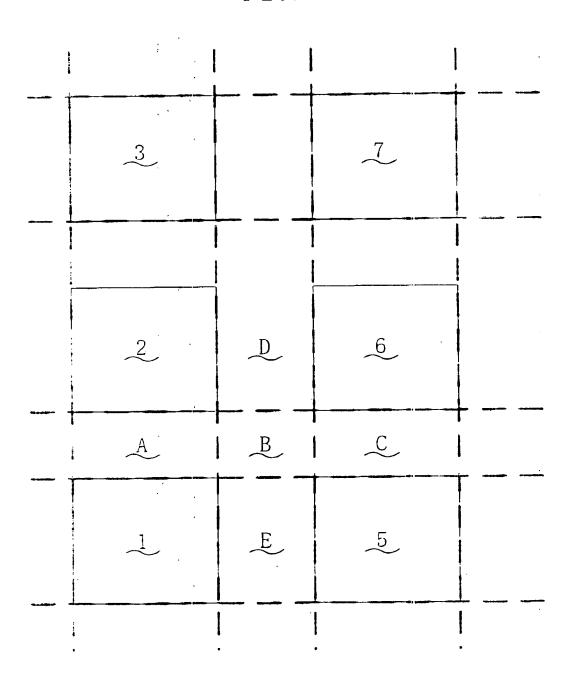

- FIG. 43 shows a layout of common circuits in pixels when each common circuit is shared by two pixels;

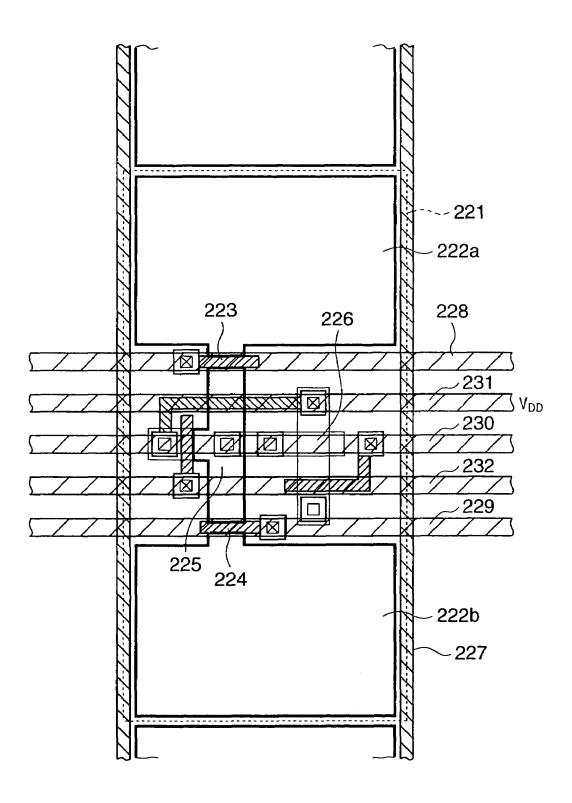

- FIG. 44 shows a practical pattern layout of two photo-55 diodes and an amplifier shown in FIG. 43;

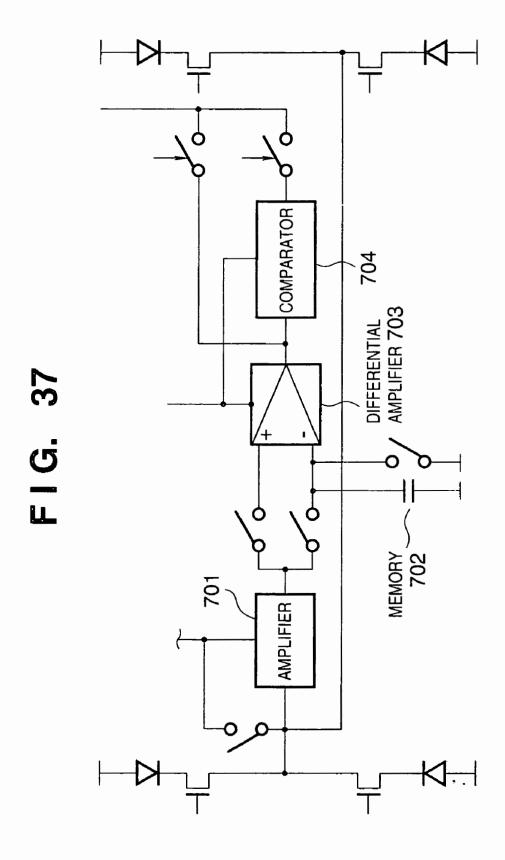

- FIGS. 45A and 45B shows color filter arrangements;

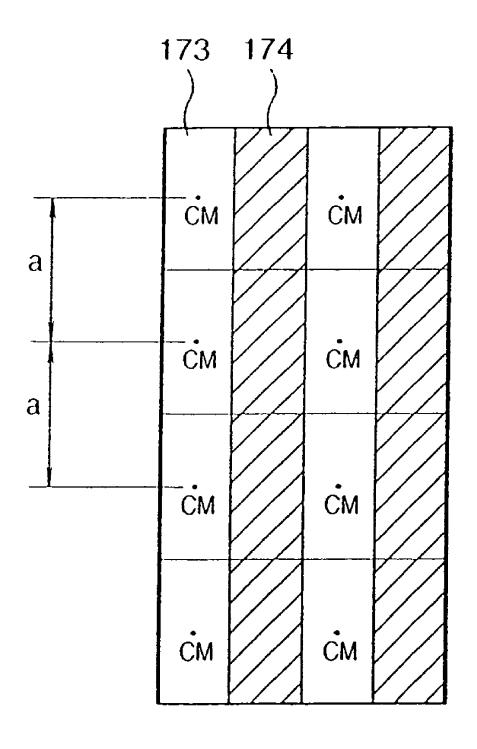

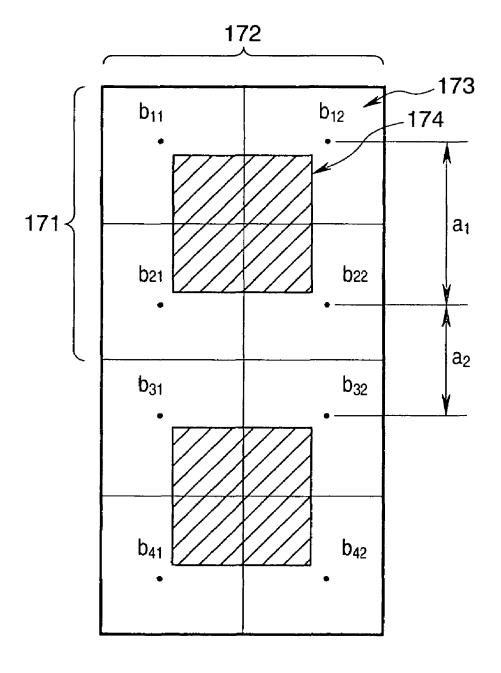

- FIG. 46 is a layout of common circuits in pixels when each common circuit is shared by four pixels; and

- FIG. 47 shows a practical pattern layout of four photo-60 diodes and an amplifier.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

Preferred embodiments of the present invention will be described in detail below in accordance with the accompanying drawings.

#### App. 0709

5

<Possible Arrangements of Pixels and Common Circuit> First, possible arrangements of a plurality of pixels and a common circuit, shared by the pixels, based on the disclosure of the Japanese Patent Application Laid-Open Nos. 63-100879 and 9-46596, are described below. In the following explanation, an amplifier is used as an example of the common circuit in an image sensing apparatus.

FIG. 43 shows an example of a layout of common circuits in pixels, when each common circuit is shared by two pixels. In FIG. 43, a case where each amplifier, as the common 10 circuit, is shared by two pixels in two rows is shown, and, more specifically, each amplifier 204 is arranged between two photodiodes 203 above and below the row of the amplifiers 204 (such as, pairs of photodiodes a<sub>11</sub> and a<sub>21</sub>, a<sub>42</sub> and a<sub>22</sub>, a<sub>31</sub> and a<sub>41</sub>, a<sub>32</sub> and a<sub>42</sub>, and so on). Note, a 15 photodiode 203, which is a photoelectric conversion element, and one half of the amplifier 204 configure a pixel. Reference numeral 201 indicates a unit cell repeated in the column direction, and reference numeral 202 indicates the unit cell repeated in the row direction.

FIG. 44 shows a practical pattern layout of two photodiodes and an amplifier (a signal unit cell). The image sensing apparatus is a CMOS sensor, in this case.

Referring to FIG. 44, reference numeral 221 denotes the unit cell (area surrounded by a dash line), which are referred 25 to by reference numerals 201 and 202 in FIG. 43, having a size of two pixels, and repeatedly arranged in both the row and column directions. Light incidents on photodiodes 222a and 222b (areas surrounded by bold lines, correspond to the photodiode pairs  $a_{11}$  and  $a_{21}$ ,  $a_{12}$  and  $a_{22}$ ,  $a_{31}$  and  $a_{41}$ ,  $a_{32}$  and a<sub>42</sub>, and so on, shown in FIG. 43) is converted into electrical charges (photo-charges), and accumulated within the photodiodes 222a and 222b. The accumulated photo-charges are respectively transferred to a floating diffusion portion 225 (also surrounded by a bold line) via a transfer gate 223 for 35 an odd row and a transfer gate 224 for an even row, further transferred to the gate (floating gate) 226 of a MOS-type amplifier, which is the amplifier 204. Current flowing through the MOS-type amplifier is modulated, and the output current is taken out from the pixel array via a vertical 40 signal line 227.

X-Y addressing of the two dimensional pixel array, as shown in FIG. 43, in the image sensing apparatus is realized by the vertical signal line 227, an odd-row scanning line 228, an even-row scanning line 229, and a row selection line 230. 45 In addition, a power line 231 for supplying electric power  $V_{DD}$  and a reset line 232 for resetting the floating diffusion portion 225 and the gate 226 to a predetermined voltage are also arranged in the horizontal direction.

The lines 228 to 232 are arranged above the wiring of the 50 unit cells, and the lines are basically wide. The area under these five opaque lines 228 to 232 does not receive light, therefore, the amplifier 204 is arranged under the lines 228 to 232. For the above reason, the two photodiodes sharing the amplifier are considered to be arranged on the upper and 55 lower sides of the amplifier.

With this layout, however, since the centers of mass (CM) of the photodiodes are not equal, as seen in FIG. 43, the following problems arise.

First, if the pixel array outputs signals of a single color, 60 since spatial frequency and resolution are different in one part from the other, the resolution deteriorates, and moreover, moiré appears.

It is possible to cover the pixel array with a color filter whose color arrangement is as shown in FIG. **45A** or **45B**. 65 In designing the color filter, colors may be arranged so that difference between intervals between pixels corresponding

6

to each color is minimized. In this case, however, the color arrangement is strictly limited.

Further, if the Bayer filter as shown in FIG. 45A is used, intervals between pixels corresponding to green (G) filter, which contributes most to luminance (Y) signals that the human eye is most sensitive to, are not equal. More specifically, considering the positions of the photodiodes, e.g.,  $a_{12}$ ,  $a_{23}$ , and  $a_{32}$  corresponding to the green filter, the distance between the photodiodes  $a_{12}$  and  $a_{23}$  in the column direction is different from the distance between the photodiodes  $a_{23}$  and  $a_{32}$  in the column direction. Thus, the filter arrangement causes different intervals between pixels corresponding to green filter, resulting in a moiré problem; therefore, the quality of an obtained image is not good.

Next, referring to FIG. 46, an example of a layout of common circuits in pixels when each common circuit is shared by four pixels, is explained.

In this case, an amplifier, i.e., the common circuit, is shared by adjoining four pixels in two rows and two columns 20 (2×2), and each amplifier 174 is surrounded by four photodiodes 173 (such as 2×2 photodiodes b<sub>11</sub>, b<sub>12</sub>, b<sub>21</sub>, and b<sub>22</sub>, and b<sub>31</sub> b<sub>32</sub>, b<sub>41</sub>, and b<sub>42</sub>). In FIG. 46, reference numeral 171 indicates a unit cell repeated in the column direction, and reference numeral 172 indicates the unit cell repeated in the 25 row direction.

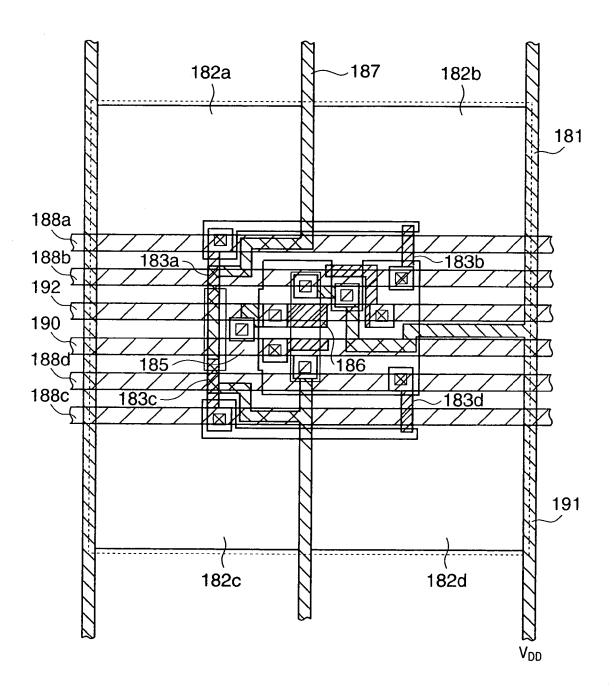

FIG. 47 shows a practical pattern layout of four photodiodes and an amplifier. The image sensing apparatus is a CMOS sensor in this case, too.

Referring to FIG. 47, reference numeral 181 denotes the unit cell (area surrounded by a dash line), which is referred to by reference numerals 171 and 172 in FIG. 46, having a size of four pixels, and repeatedly arranged in both the row and column directions. Light incidents on photodiodes 182a to 182d (correspond to either one of groups of the photodiodes,  $b_{11}$ ,  $b_{12}$ ,  $b_{21}$ , and  $b_{22}$ , and  $b_{31}$ ,  $b_{32}$ ,  $b_{41}$ , and  $b_{42}$ shown in FIG. 46) is converted into electrical charges (photo-charges), and accumulated within the photodiodes 182a to 182d. The accumulated charges are respectively transferred to a floating diffusion portion 185 via transfer gates 183a to 183d, respectively, further transferred to the gate 186 of a MOS-type amplifier, which is the amplifier 174. Current flowing through the MOS-type amplifier is modulated, and the output current is taken out from the pixel array via a vertical signal line 187.

X-Y addressing of the two dimensional pixel array, as shown in FIG. 46, in the image sensing apparatus is realized by the vertical signal line 187, scanning lines 188a to 188d, and a row selection line 190. In addition, a power line 191 for supplying electric power  $V_{DD}$  is arranged in the column direction, and a reset line 192 for resetting the floating diffusion portion 185 and the gate 186 to a predetermined voltage are arranged in the horizontal direction.

The lines 188 to 192 are arranged above the wiring of the unit cells, and the lines are basically wide. The area under these six opaque lines 188 to 192 does not receive light, therefore, the amplifier 174 is arranged under the lines 188 to 182. For the above reason, the four photodiodes sharing the amplifier are considered to be arranged around the amplifier.

With this layout, however, since the intervals between the centers of mass (CM) of photodiodes are not equal, as seen in FIG. **46**, the following problem arises.

If the pixel array outputs signals of a single color, since spatial frequency and resolution are different in one part from another, the resolution deteriorates, and moreover, moiré appears. The moiré is a serious problem, and an image sensing apparatus with a moiré problem does not sell on the

7

market. This can be said for any image sensing apparatus having a configuration in which any number of pixels share a single common circuit.

Accordingly, the inventors of the present application have developed image sensing apparatuses having improved arrangements of pixels and circuits shared by a plurality of pixels.

The image sensing apparatuses will be described below in detail.

<Basic Configuration of Image Sensing Apparatus>

FIG. 1 is a block diagram illustrating a configuration of the image sensing apparatus according to an embodiment of the present invention.

As shown in FIG. 1, light incoming through an optical system 21 forms an optical image on a CMOS sensor 22, and converted into electric charges by a pixel array arranged on the CMOS sensor. The photo-charges are further converted, processed and outputted by a signal processing circuit 23 in a predetermined method. The processed signals are recorded on an information storage medium or outputted by a recording/transmission system 24. The recorded or transmitted information is retrieved by a retrieving system 27. The CMOS sensor 22 and the signal processing circuit 23 are controlled by a timing controller 25, and the optical system 21, the timing controller 25, the recording/transmission system 24, and the retrieving system 27 are controlled by a system controller 26.

Next, the CMOS sensor 22 according to the present <sup>30</sup> invention will be described in detail.

#### First Embodiment

FIG. 2A shows a layout of amplifiers 12 in pixels when each amplifier 12 is shared by two pixels adjoining in the column direction, and FIG. 2B shows a layout of amplifiers 12 in pixels when each amplifier 12 is shared by two pixels adjoining in the row direction.

In FIG. 2A, two photoelectric conversion elements 11 (such as, pairs of the elements P<sub>11</sub>, and P<sub>21</sub>, P<sub>31</sub> and P<sub>41</sub>, P<sub>12</sub> and P<sub>22</sub>, P<sub>32</sub> and P<sub>42</sub>, and so on) sharing one amplifier 12 are arranged next to each other in the column direction, and the amplifier 12 is arranged along the adjoining pixels. In this manner, intervals between the centers of mass of the photoelectric conversion elements 11 (e.g., P<sub>11</sub>, P<sub>21</sub>, P<sub>31</sub>, P<sub>41</sub>, P<sub>12</sub>, P<sub>22</sub>, P<sub>32</sub>, P<sub>42</sub>) in both the row and column directions become equal. Reference numeral 13 indicates a unit cell repeated in the column direction, and reference numeral 14 indicates the unit cell repeated in the row direction.

Further, in FIG. 2B, two photoelectric conversion elements 11 (such as, pairs of the elements P<sub>11</sub> and P<sub>12</sub>, P<sub>13</sub> and P<sub>14</sub>, P<sub>21</sub> and P<sub>22</sub>, P<sub>23</sub> and P<sub>24</sub>, P<sub>31</sub> and P<sub>32</sub>, P<sub>33</sub> and P<sub>34</sub>, and so on) sharing one amplifier 12 are arranged next to each other in the row direction, and the amplifier 12 is arranged along the adjoining pixels. In this manner, intervals between the centers of mass of the photoelectric conversion elements 11 (P<sub>11</sub>, P<sub>12</sub>, P<sub>13</sub>, P<sub>14</sub>, P<sub>21</sub>, P<sub>22</sub>, P<sub>23</sub>, P<sub>24</sub>, P<sub>31</sub>, P<sub>32</sub>, P<sub>33</sub>, P<sub>34</sub>) in both the row and column directions also become equal. Reference numeral 15 indicates a unit cell repeated in the column direction, and reference numeral 16 indicates the unit cell repeated in the row direction.

In the first embodiment, the number, N, of photoelectric conversion elements 11 sharing each amplifier 12 is two (N=2), however, the number N may be an arbitrary number greater than 2.

8

[Layout 1]

FIG. 3 shows a practical pattern layout of two photodiodes and an amplifier in the CMOS sensor 22, and FIG. 4 is a brief view of FIG. 3 from which a part of lines are omitted.

The CMOS sensor, as shown in FIG. 3, is formed on a singlecrystalline silicon substrate based on a layout rule 0.4  $\mu$ m. Each pixel is a square, 8  $\mu$ m each side, and a source follower amplifier, as the amplifier 12, is shared by two adjoining pixels arranged in the column direction. Therefore, the size of a unit cell 31, shown by a dash line and is referred to by reference numerals 13 and 14 in FIG. 2A, is 8  $\mu$ m×16  $\mu$ m. A plurality of unit cells 31 are arranged in two dimensions.

The photodiodes 32a and 32b, i.e., the photoelectric conversion elements, are formed on the right portion of respective pixels, and the shapes of the photodiodes 32a and 32b are almost mirror images. Further, the photodiodes 32a and 32b are designed so that the center of masses (CM) of light-receiving areas of the photodiodes 32a and 32b are located at a substantially identical position of each pixel. In FIG. 3, the areas of the photodiodes 32a and 32b, and the area of a floating diffusion (FD) portion 35 are shown by bold lines. Further, in FIG. 3, reference numeral 38 denotes an odd-row scanning line for controlling each transfer gate 33 in an odd-number row; 39, an even-row scanning line for controlling each transfer gate 34 in an even-number row; 40, a row selection line; and 42, a reset line for controlling the gate 43 of a MOS transistor. In FIG. 4, the lines 38 to 42 are not shown.

Photo-charges accumulated in the photodiodes 32a and 32b are transferred to the FD portion 35 via the transfer gate 33 for the odd-number row and the transfer gate 34 for the even-number row. The size of the both transfer gates 33 and 34 is L=0.4 µm, W=1.0 µm (L is a channel length and W is a channel width). The FD portion 35 is connected to the gate 36 of a source follower via an aluminum (Al) wire having a width of 0.4 µm, and the photo-charge transferred to the FD portion 35 modulates the gate voltage of the gate 36. The 40 size of the MOS transistor of the gate 36 is L=0.8 µm, W=1.0 µm, and the total capacitance of the FD portion 35 and the gate 36 is about 5 fF. Since Q=CV; the gate voltage of the gate 36 changes by 3.2 volts in response to the transference of 10<sup>5</sup> electrons.

Current flowing in from a  $V_{DD}$  terminal 41 is modulated by the MOS transistor of the gate 36, and transferred to a vertical signal line 37. Current flowing through the vertical signal line 37 is processed by a signal processing circuit (not shown) and formed into image information.

Thereafter, in order to set the potentials of the photodiodes 32a and 32b, the FD portion 35, and the gate 36 to the predetermined potential  $V_{DD}$ , the gate 43 of the MOS transistor connected to the reset line 42 is opened (at this time, the transfer gate 33 for the add-number row and the transfer gate 34 for the even-number row are also opened), thereby the photodiodes 32a and 32b, the FD portion 35, and the gate 36 are electrically connected to the  $V_{DD}$  terminal 41.

Thereafter, the transfer gates 35 and 36 are closed, thereby the accumulation of photo-charges in the photodiodes 32a and 32b start again.

The total number of the lines arranged in each unit cell in the horizontal direction is four, specifically, the odd-row scanning line 38, the even-row scanning line 39, the row selection line 40, and the reset line 42. The four lines are arranged in such a manner that two lines each are arranged on the upper and lower ends of each pixel, as shown in FIG.

9

Since these lines are thick wires and provided over pixels, as described above, an increase in the number of lines results in an increase in area which can not receive light, which reduces aperture. Further, if the number of lines provided over a row is different from the number of lines arranged over another row, such that two lines in one row and three lines in the other row, the apertures and the centers of mass of photodiodes adjoining in the column direction become different in one row from the other.

In layout 1, the power supply voltage  $V_{DD}$  is provided to  $^{10}$  every pixel by connecting a power supply (not shown) with each pixel via a metal light-shield layer (not shown), arranged on the top layer of the CMOS sensor, and the  $V_{DD}$  terminal 41, formed as a through hole, in order to avoid the problem described in the previous paragraph.  $^{15}$

With the layout 1 as described above, it is possible to provide a CMOS sensor having a plurality of pixels, arranged in the same interval from each other, which have relatively high area ratio or high aperture.

It should be noted that the area ratio or aperture may be further increased by using known on-chip convex lenses, for instance.

Further, the metal layer used for supplying the power supply voltage  $V_{DD}$  is not limited to a light-shield film, and may be an electrode material used for forming capacitor, for instance, placed over the entire pixel.

[Layout 2]

FIG. 5 shows another practical pattern layout of two photodiodes and an amplifier in the CMOS sensor 22, and 30 FIG. 6 is a brief view of FIG. 5 from which several lines are omitted. Further, FIGS. 7 and 8 are enlarged views showing vicinity of an FD portion. Specifically, FIG. 7 is a view when a wire over a gate 54 is omitted, and FIG. 8 is a view when a wire is provided-over the gate 54.

Referring to FIGS. 6 to 8, the areas of photodiodes 52a and 52b, and an FD portion 55 are shown by bold lines. The layout 2 also shows a case where two adjoining pixels share a single amplifier, similarly to the layout 1, but the two adjoining pixels are arranged in the row direction. The 40 centers of mass of the two adjoining photodiodes are located at a substantially same position of the each photodiode.

Referring to FIGS. 5 and 6, reference numerals 52a and 52b are the photodiodes; 53, a transfer gate for an odd-number column; 54, a transfer gate for an even-number column; 55, the FD portion; 56, the gate of a source follower; 57, a vertical signal line; 58, an odd-column scanning line for controlling the transfer gate 53 in an odd-number column; 59, an even-column scanning line for controlling the transfer gate 54 in an even-number column; 50, a row selection line; and 62, a reset line for controlling the gate 63 of a MOS transistor. Note, a wire connecting the gate 56 of the source follower and the FD portion 55 crosses over the gate 54 as shown in FIG. 8.

In layout **2**, the area ratio or the aperture is improved comparing to the layout **1** in which sharing an amplifier with two pixels adjoining in the column direction. Accordingly, a CMOS sensor of wide dynamic range, high sensitivity, and high S/N ratio is realized.

In layout 2, necessary four lines are arranged, and a power supply line 61 for providing a voltage  $V_{DD}$  is arranged in the column direction on the side of photodiodes opposite to the side of the vertical signal line 57.

[Noise Reduction]

The inventors of the present application also have developed a signal read circuit, for reducing noise, suitably used

10

in an image sensing apparatus having a configuration, as described above, in which a plurality of pixels share an amplifier

The noise reduction operation is explained with reference to FIGS. 9 and 10.

FIG. 9 shows a circuit configuration of a unit cell of a CMOS sensor in which two photoelectric conversion elements share one amplifier. Referring to FIG. 9, PD1 and PD2 denote photodiodes as photoelectric conversion elements;  $M_{TX1}$  and  $M_{TX2}$ , MOS transistors for transferring photocharges accumulated in the photodiodes PD1 and PD2 to an FD portion;  $M_{RES}$ , a MOS transistor for resetting the FD portion; and  $M_{SF}$  and  $M_{SEL}$ , MOS transistors configuring a source follower. The MOS transistor  $M_{SEL}$  also functions as a selection switch for selecting a photodiode.

First, reset operation is performed by turning on the MOS transistor M<sub>RES</sub>, then, noise signal is read out from the MOS transistors  $M_{SF}$  and  $M_{SEL}$  configuring the source follower. Next, photo-charge accumulated in the photodiode PD1 is transferred to the gate of the MOS transistor  $M_{SF}$  via the MOS transistor  $M_{TX1}$ , then read out as a first signal via the MOS transistors  $M_{SF}$  and  $M_{SEL}$ . Thereafter, reset operation is performed again, and photo-charge accumulated in the photodiode PD2 is transferred to the gate of the MOS transistor  $M_{SF}$  via the MOS transistor  $M_{TX2}$ , then read out as a second signal via the MOS transistors  $M_{SF}$  and  $M_{SEL}$ . Accordingly, the noise signal, the first signal, and the second signal are obtained, and, by subtracting the noise signal from the first and second signals, a signal corresponding to the photodiode PD1 without the noise component as well as a signal corresponding the photodiode PD2 without the noise component are obtained.

Further, it is possible to add the photo-charge signal corresponding to the photodiode PD1 and the photo-charge signal corresponding to the photodiode PD2 by transferring photo-charge accumulated in the photodiode PD2 to the gate of the MOS transistor  $M_{SF}$  while photo-charge accumulated in the photodiode PD1 is kept at the gate of the MOS transistor  $M_{SF}$  by changing operation timing.

Next, the image sensing apparatus including a signal processing circuit according to the first embodiment will be explained below. FIG. 10 shows an equivalent circuit of the image sensing apparatus including the signal processing circuit according to the first embodiment, and FIGS. 11 and 12 are timing charts for operating the apparatus.

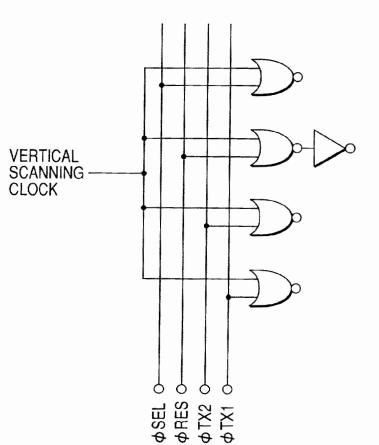

Referring to FIGS. 10 and 11, vertical scanning operation is initiated in response to the pulse, which indicates a vertical blanking period, of a signal  $\phi V_1$  or  $\phi V_2$ . First, a signal  $\phi TX_{RO-1}$  which is applied to the reset line 62 of the first row is activated during a horizontal blanking period (i.e., when a signal  $\phi HBL$  is high), and signals  $\phi TX_{RO-i}$  (i is a row number. Below, the last part of the subscript, -i, is omitted.) for subsequent lines are activated in the same manner. Accordingly, all the pixels in every row are reset to the reset potential  $V_{DD}$ .

In each horizontal blanking period, during a period  $T_1$ , a signal  $\phi$ L becomes high and a transistor 81, connected to the vertical signal line 57, is turned on and the vertical signal line 57 is reset. Simultaneously, signals  $\phi T_N$ ,  $\phi T_{S1}$  and  $\phi T_{S2}$  also become high, and transistors 82-1, 82-2, and 82-3 are turned on. Accordingly the upstream part of transistors for reading signals, 84-1, 84-2, and 84-3, and capacitors 83-1, 83-2, and 83-3 ( $C_{TN}$ ,  $C_{TS1}$ ,  $C_{TS2}$ ) are electrically connected to the vertical signal line 57, and reset. Accordingly, residual charges in the capacitors 83-1, 83-2, and 83-3, for instance, are removed.

11

Thereafter, in a period  $T_2$ , the signal  $\phi TX_{R0}$  to be applied to the reset line 62 is changed to high, and the floating gate, which is the gate of the source follower amplifier configured with the MOS transistors  $M_{SF}$  and  $M_{SEL}$  in each unit cell, is reset to the voltage  $V_{DD}$ .

Then, in a period  $T_3$ , a signal  $\phi RV$  becomes high and a transistor 80 for grounding, connected to the vertical signal line 57, is turned on, and the vertical signal line 57 is grounded. Simultaneously, the signal  $\phi T_N$  is changed to high in order to connect the capacitor 83-1 ( $C_{TN}$ ) for storing a 10 noise component to the vertical signal line 57, and the transistor 82-1 is turned on. At this time, a signal  $\phi S_O$  to be applied to the row selection line 60 is high, and current corresponding to the potential (about  $V_{DD}$ ) at the floating gate of the MOS transistor  $M_{SF}$  flows from the  $V_{DD}$  terminal **41** to the capacitor **83-1** ( $C_{TN}$ ), thereby the capacitor **83-1**  $(C_{TN})$  stores charge corresponding to the noise component.

Next, in a period  $T_4$ , a signal  $\phi TX_{OO}$  applied to the odd-column scanning line 58 is changed to high, in turn, the transfer gate (MOS transistor  $M_{TX1}$ , in this case) in an odd-number column is turned on, and photo-charge accumulated in the photodiode PD1 is transferred to the floating gate of the MOS transistor  $M_{SF}$ . The capacitor 83-1 ( $C_{TN}$ ) for storing the noise component is disconnected from the vertical signal line 57 when the signal  $\phi T_N$  becomes low, and the capacitor 83-2 ( $C_{TS1}$  for storing a photo-charge signal is connected, in turn, when the signal  $\phi T_{S1}$  is changed to high. Thus, charge accumulated in the photodiode PD1, for instance, in an odd-number column is stored in the capacitor **83-2** ( $C_{TS1}$ ) via the vertical signal line **57**.

Next, in a period T<sub>5</sub>, the signal φL becomes high, and only the vertical signal line 57 is reset. Since the signals  $\phi S_O$ ,  $\phi T_N$ ,  $\phi T_{S1}$  and  $\phi T_{S2}$ , are low, other portions are not reset, and their states are preserved.

Next, the signal  $\phi TX_{RO}$  applied to the reset line 62 is changed to high between periods  $T_5$  and  $T_6$ , and the gate of the source follower amplifier (i.e., the gate of MOS transistor  $M_{SF}$ ) is reset to the potential  $V_{DD}$ .

In the period  $T_6$ , a signal  $\phi TX_{Qe}$  applied to the evencolumn scanning line 59 is changed to high, and photocharge accumulated in the photodiode PD2 in an evennumber column is transferred to the floating gate of the MOS transistor  $M_{SF}$ . At this time, the signal  $\phi T_{S2}$  is changed to high, thus the capacitor 83-3 ( $C_{TS2}$ ) for storing another photo-charge signal is electrically connected to the vertical signal line 57, and photo-charge accumulated in the photodiode PD2, for instance, in an even-number column is stored in the capacitor 83-3 ( $C_{TS2}$ ) via the vertical signal line 57.

In the aforesaid manner, charges corresponding to the 50 noise component, a first signal, and a second signal are respectively stored in the capacitors 83-1, 83-2, and 83-3  $(C_{TN}, C_{TS1}, C_{TS2})$  by each column for a row.

Next, in a period T<sub>7</sub>, in order to sequentially transfer the charges stored in the capacitors 83-1, 83-2, and 83-3 ( $C_{TN}$ , 55 C<sub>TS1</sub>, C<sub>TS2</sub>) to amplifiers 86-1 to 86-3, respectively, a horizontal scanning signal φHn is changed to high for each columns controlled by a horizontal shift register 71, and transistors 84-1 to 84-3, provided for each column, are  $C_{TS2}$ ) are connected to the respective amplifiers 86-1 to **86-3**. From the capacitors **83-1** to **83-3** ( $C_{TN}$ ,  $C_{TS1}$ ,  $C_{TS2}$ ), the noise component, the first signal, and the second signal are outputted, and from a differential amplifier 87-1, a signal S1 obtained by subtracting the noise component from the first 65 signal is outputted, and a signal S2 obtained by subtracting the noise component from the second signal is outputted

12

from a differential amplifier 87-2. Note that accumulation of photo-charges in the photodiodes is also performed during

In a case where the signal  $\phi TX_{RO}$  to be applied to the reset line 62 between the period  $T_5$  and the period  $T_6$  is not changed to high and reset operation is not performed, photo-charge generated by the photodiode PD2 in an evennumber column is transferred to the floating gate of the MOS transistor  $M_{SF}$  where photo-charge generated by the photodiode PD1 remains; accordingly, a signal of the photodiode PD1 in the odd-number column and a signal of the photodiode PD2 in the even-number row are stored in the capacitor 83-3 ( $C_{TS2}$ ) via the vertical signal line 57. Therefore, a noise component, a signal corresponding to one photodiode (single signal component), and a signal corresponding to two photodiodes (double signal component) are stored in the capacitors 83-1 to 83-3 ( $C_{TN}$ ,  $C_{TS1}$ ,  $C_{TS2}$ ). Then, the noise component, the single signal component, and the double signal component are outputted to the amplifiers 86-1 to 86-3 during the period  $T_7$ . Thereafter, the noise component is subtracted from the single signal component by the differential amplifier 87-1 and a signal S1 is outputted. Similarly, the noise component is subtracted from the double signal component by the differential amplifier 87-2 and a signal S2 is outputted.

Further, the first embodiment of the present invention is not limited to two-dimensional array, and capable of applying to an one-dimensional line sensor.

According to the first embodiment as described above, it is possible to realize a high precision image sensor without causing deterioration of performance, such as deterioration of resolution and generation of moiré, for instance. In addition, yield of image sensing apparatus becomes high.

#### Second Embodiment

Next, the second embodiment of the present invention will be explained.

FIGS. 13 and 14 show other layouts of amplifiers 12, as 40 common circuits, and photodiodes 11 when each amplifier 12 is shared by two photodiodes 11.

As shown in FIG. 13, the photodiodes 11 are arranged so that adjoining rows are shifted from each other by one half pitch. In odd-number rows, pixels covered by green (G) filter (referred to as "G pixel" hereinafter), which contribute mainly to a luminance (Y) signal, are respectively set across the amplifiers from pixels covered by red (R) filter (referred to as "R pixel" hereinafter), which contribute to a colordifference signal, and in even-number rows, G pixels are respectively set across the amplifiers from pixels covered by blue (B) filter (referred to as "B pixel" hereinafter), which also contributes to a color-difference signal. By arranging the G pixels in adjoining rows, shifted by one and half pitches in the row direction, intervals between G pixels in the row direction becomes the same, further, intervals between the G pixels in the column direction also become the same. Accordingly problem of moiré is solved, and a sensed image does not look deteriorated.

Further, FIG. 14 shows an example when photodiodes 11 turned on; thereby the capacitors 83-1 to 83-3 (C<sub>TN</sub>, C<sub>TS1</sub>, 60 are arranged so that adjoining columns are shifted from each other by one half pitch.

> Next, FIG. 15 shows a practical pattern layout of two photodiodes and an amplifier, as the common circuit, shared by the two photodiodes 11 arranged on right and left sides of the amplifier 12, as shown in FIG. 13.

> The CMOS sensor, as shown in FIG. 15, is formed on a singlecrystalline silicon substrate. Each pixel is a square, 8

13

$\mu$ m each side, shown by a dash line 341. As described above, plural pairs of photodiodes are arranged in a two-dimensional array. Between each pair of two photodiodes, the common circuit is arranged. A photodiode covered by G filter (G photodiode) is set on the left side of the common 5 circuit, and a photodiode covered by R or B filter (R/B photodiode) is set on the right side of the common circuit. In FIG. 15, an amplifier, using MOS transistors, is used as the common circuit, as an example. The layout rule is 0.4  $\mu$ m, and an area, area ratio, an aperture area, and aperture 10 ratio of a photodiode 342 as a photoelectric conversion element is 57.96  $\mu$ M<sup>2</sup>, 60.4%, 28.88  $\mu$ m<sup>2</sup> and 30.1%, respectively. These figures are very high comparing to conventional figures.

Reference numeral 343 denotes a transfer gate for trans- 15 ferring photo-charge from a G photodiode 342 to a floating diffusion (FD) portion 345 and reference numeral 344 denotes a transfer gate for transferring photo-charge from an R/B photodiodes 342' also to the FD portion 345. The channel length and the channel width of each MOS transistor is 0.4  $\mu$ m and 1.0  $\mu$ m, respectively. Reference numeral 347 denotes a reset gate for resetting the FD portion 345 to a potential of a power supply voltage  $V_{DD}$  through a terminal 350, and reference numeral 346 denotes a gate of a MOS- 25 type source follower amplifier. The potential of the gate 346 changes depending upon the transferred charge, and the amplifier modulates current flowing in from the  $V_{DD}$  terminal 350.

The total capacitance of the FD portion 345 and the gate 30 **346** is about 10 fF, and as the area of the photodiodes increases, the capacitance also increases. The modulated current is eventually outputted to a vertical signal line 349 via a selection gate 348 for selectively outputting the cur-

Further, reference numerals 351 to 354 denote scanning lines for applying a predetermined potential to the selection gate 348, the transfer gates 343 and 344, and the reset gate 347, respectively.

[Noise Reduction]

Next, signal processing for reducing noise preferably used in the above-described image sensor is explained.

FIG. 16 is an equivalent circuit diagram according to the second embodiment. In FIG. 16, the same units and elements as those shown in FIGS. 10 and 15 are referred to by the 45 same reference numerals. Further, FIG. 17 is an equivalent circuit diagram of a unit cell 374, surrounded by a dash line in FIG. 16 and whose pattern layout is shown in FIG. 15, configured with a common circuit 372 and photodiodes arranged on the both sides of the common circuit 372.

In FIG. 17, reference numeral 350 is the  $V_{DD}$  terminal; 345, the FD portion; 363, a reset unit, such as a MOS transistor (reset MOS), for resetting the FD portion 345; 364 and 364', transfer units, such as MOS transistors (transfer MOS), for transferring photo-charges from the photodiodes 55 342 and 342' to the FD portion 345; 365, an amplifier, such as a MOS transistor, for amplifying the change in the potential at the FD portion 345; and 366, a MOS transistor for selection (selection MOS) for selectively outputting a Further, the scanning lines 354, 351, 352 and 353 are for applying potentials for turning on or off the reset MOS 363, the selection MOS 366, the transfer MOS 364, and the transfer MOS 364', respectively. In the unit cell 374, the MOS transistors 363, 364, 364', 365, and 366 configure the common circuit. Further, in the pattern layout shown in FIG. 15, the transfer gate 343 corresponds to the gate of the

14

transfer MOS 364 of FIG. 17, the transfer gate 344 corresponds to the gate of the transfer MOS 364', the reset gate 347 corresponds to the gate of the reset MOS 363, and the selection gate 348 corresponds to the gate of the selection MOS 366.

Next, referring to the circuit diagrams shown in FIGS. 16 and 17, and timing charts shown in FIGS. 11 and 12, the noise reduction operation is explained.

Referring to FIG. 11, vertical scanning operation is initiated in response to the pulse, which indicates a vertical blanking period, of a signal  $\phi V_1$  or  $\phi V_2$ . First, a signal  $\phi TX_{RO-1}$  which is applied to the reset line 354 of the first row is activated during a horizontal blanking period (i.e., when a signal  $\phi$ HBL is high), and signals  $\phi$ TX<sub>RO-i</sub> (i is a row number. Below, the last part of the subscript, -i, is omitted.) for subsequent lines are applied in the same manner. Accordingly, all the pixels in every row are reset to the reset potential  $V_{DD}$ .

In each horizontal blanking period, during a period  $T_1$ , a transfer gates 343 and 344 are MOS transistors, and the 20 signal  $\phi$ L becomes high, as shown in FIG. 12, and a transistor 81, connected to the vertical signal line 349, is turned on and the vertical signal line 349 is reset. Simultaneously, signals  $\phi T_N$ ,  $\phi T_{S1}$  and  $\phi T_{S2}$  also become high, and transistors 82-1, 82-2, and 82-3 are turned on. Accordingly wires in the upstream of transistors for reading signals, 84-1, **84-2**, and **84-3**, and capacitors **83-1**, **83-2**, and **83-3** ( $C_{TN}$ ,  $C_{TS1}$ ,  $C_{TS2}$ ) are electrically connected to the vertical signal line 349, and reset. Accordingly, residual charge in the capacitors 83-1, 83-2, and 83-3, for instance, are removed.

Thereafter, in a period  $T_2$ , the signal  $\phi TX_{R0}$  to be applied to the reset line 354 is changed to high, and the floating gate, which is the gate of the source follower amplifier configured with the MOS transistors 365 and 366 in each unit cell is reset to the voltage  $V_{DD}$ .

Then, in a period T<sub>3</sub>, a signal  $\phi RV$  becomes high and a transistor 80 for grounding, connected to the vertical signal line 349, is turned on, and the vertical signal line 349 is grounded. Simultaneously, the signal  $\phi T_N$  is changed to high in order to connect the capacitor 83-1 (C<sub>TN</sub>) for storing a 40 noise component to the vertical signal line 349, and the transistor 82-1 is turned on. At this time, a signal  $\phi S_Q$  to be applied to the row selection line 351 is high, and current corresponding to the potential (about  $V_{DD}$ ) at the floating gate of the MOS transistor 365 flows from the  $V_{DD}$  terminal **350** to the capacitor **83-1** ( $C_{TN}$ ), thereby the capacitor **83-1**  $(C_{TN})$  stores charge corresponding to the noise component.

Next, in a period  $T_4$ , a signal  $\phi TX_{OO}$  applied to the G pixel scanning line 353 is changed to high, in turn, transfer gate (MOS transistor 364) for the G pixel is turned on, and photo-charge accumulated in the photodiode 342 is transferred to the floating gate of the MOS transistor 365. The capacitor 83-1 ( $C_{TN}$ ) for storing the noise component is disconnected from the vertical signal line 349 when the signal  $\phi T_N$  becomes low, and the capacitor 83-2 ( $C_{TS1}$ ) for storing a photo-charge signal is connected, in turn, when the signal  $\phi T_{\mathcal{S}1}$  is changed to high. Thus, charge accumulated in the G photodiode 342, for instance, is stored in the capacitor 83-2 ( $C_{TS1}$ ) via the vertical signal line 349.

Next, in a period  $T_5$  the signal  $\phi L$  becomes high, and only signal from the amplifier 365 to the vertical signal line 349. 60 the vertical signal line 349 is reset. Since the signals  $\phi S_O$ ,  $\phi T_N$ ,  $\phi T_{S1}$ , and  $\phi T_{S2}$  are low, other portions are not reset, and their states are preserved.

> Next, the signal  $\phi TX_{RQ}$  applied to the reset line 354 is changed to high between periods T<sub>5</sub> and T<sub>6</sub>, and the FD portion 345 is reset to the potential  $V_{DD}$ .

> In the period  $T_6$ , a signal  $\phi TX_{Oe}$  applied to the R/B pixel scanning line 352 is changed to high, and photo-charge

15

accumulated in the R/B photodiode **342**' is transferred to the floating gate of the MOS transistor **365**. At this time, the signal  $\phi T_{S2}$  is changed to high, thus the capacitor **83-3** ( $C_{TS2}$ ) for storing another photo-charge signal is electrically connected to the vertical signal line **349**, and charge accumulated in the R/B photodiodes **342**', for instance, is stored in the capacitor **83-3** ( $C_{TS2}$ ) via the vertical signal line **349**.

In the aforesaid manner, charges corresponding to the noise component, a first signal, and a second signal are respectively stored in the capacitors 83-1, 83-2, and 83-3 ( $C_{TN}$ ,  $C_{TS1}$ ,  $C_{TS2}$ ) by each column for a row.

Next, in a period T<sub>7</sub>, in order to sequentially transfer the charges stored in the capacitors 83-1, 83-2, and 83-3 ( $C_{TN}$ ,  $C_{TS1}$ ,  $C_{TS2}$ ) to amplifiers 86-1 to 86-3, respectively, a 15 horizontal scanning signal \$\phi\$Hn is changed to high for each columns controlled by a horizontal shift register 71, and transistors 84-1 to 84-3, provided for each column, are turned on; thereby the capacitors 83-1 to 83-3 ( $C_{TN}$ ,  $C_{TS1}$ ,  $C_{TS2}$ ) are connected to the amplifiers 86-1 to 86-3. From the  $^{20}$ capacitors 83-1 to 83-3 ( $C_{TN}$ ,  $C_{TS1}$ ,  $C_{TS2}$ ), the noise component, the first signal, and the second signal are outputted, and from a differential amplifier 87-1, a G component signal obtained by subtracting the noise component from the first signal is outputted, and an R/B component signal obtained by subtracting the noise component from the second signal is outputted from a differential amplifier 87-2. Note that accumulation of photo-charges in the photodiodes is also performed during the period  $T_7$ .

In a case where the signal  $\phi TX_{RO}$  to be applied to the reset line 354 between the period  $T_5$  and the period  $T_6$  is not changed high and reset operation is not performed, photocharge generated by the R/B photodiodes 342' is transferred to the floating gate of the MOS transistor 365 where photo- 35 charge generated by the G photodiode 342 remains; accordingly, a signal of the G photodiode 342 and a signal of the R/B photodiode 342' are stored in the capacitor 83-3 ( $C_{TS2}$ ) via the vertical signal line 349. Therefore, a noise component, a signal corresponding to one photodiode (single signal 40 component), and a signal corresponding to two photodiodes (double signal component) are stored in the capacitors 83-1 to 83-3 ( $C_{TN}$ ,  $C_{TS1}$ ,  $C_{TS2}$ ). Then, the noise component, the single signal component, and the double signal component are outputted to the amplifiers 86-1 to 86-3 during the period 45  $T_7$ . Thereafter, the noise component is subtracted from the single signal component by the differential amplifier 87-1 and a G component signal is outputted. Similarly, the noise component is subtracted from the double signal component by the differential amplifier 87-2 and a G+R/B component 50 signal is outputted.

The signal processing circuit 23, shown in FIG. 1, according to the second embodiment is explained with reference to FIG. 18.

The G and R/B component signals output from the CMOS sensor 22 are converted into luminance (Y) signals and color difference  $(C_R, C_B)$  signals. Note that low frequency component of the luminance signals are generated using R, G, and B signals of at least two adjoining rows.

Further, high frequency component of the luminance signals are generated using high frequency component of G signals in at least two adjoining rows. Accordingly, an image of high resolution and good color reproduction is obtained.

According to the second embodiment as described above, 65 it is possible to obtain an image sensing apparatus of good sensitivity, high resolution, and wide dynamic range.

#### 16

#### Third Embodiment

Next, the third embodiment of the present invention will be explained with reference to accompanying drawings.

FIG. 19 shows a layout of amplifiers 12 in pixels when each amplifier 12 is shared by four (2 rows×2 columns) pixels, according to the third embodiment.

In FIG. 19, each amplifier 12 is arranged in the center of four pixels, and four photoelectric conversion elements 11 (e.g.,  $q_{11}$ ,  $q_{12}$ ,  $q_{21}$ ,  $q_{22}$ ) are arranged as they surround the amplifier 12.

Further, a light-shield unit 17 is provided for each pixel in an area which is symmetry to a portion of the amplifier 12 occupying the pixel with respect to the center of the pixel. Therefore, the center of mass of each photoelectric conversion element 11 is in the center of each pixel. Accordingly, the centers of mass of the photoelectric conversion elements 11 (q<sub>11</sub>, q<sub>12</sub>, q<sub>21</sub>, q<sub>22</sub>, q<sub>31</sub>, q<sub>32</sub>, q<sub>41</sub>, q<sub>42</sub>) are arranged at a same interval, D, both in the row and column directions.

FIG. 20 shows another layout of amplifiers 12 in pixels when each amplifier 12 is arranged at the boundary of four pixels arranged in a  $2\times2$  array in the row direction, and the four photoelectric conversion elements 11 (e.g.,  $q_{11}$ ,  $q_{12}$ ,  $q_{21}$ ,  $q_{22}$ ) are arranged so as to sandwich each amplifier 12.

In addition, light-shield unit 17 is arranged in three peripheral areas, other than the peripheral area where the amplifier 12 occupies, of the pixel, as shown in FIG. 20. Therefore, the centers of mass of the photoelectric conversion elements 11  $(q_{11}, q_{12}, q_{21}, q_{22}, q_{31}, q_{32}, q_{4l}, q_{42})$  are located at the same interval, D, both in the row and column directions

The arrangement as shown in FIG. 20 is rotated by 90 degrees, namely, an arrangement in which row direction and column direction are exchanged, is also possible.

Further, in an arrangement as shown in FIG. 21, G filter, which contributes most to resolution, is arranged in the upper left pixel and the lower right pixel among four pixels configuring a unit cell 30. In the pixel covered by green filter (G pixel), a light-shield unit 17 is provided in an area which is symmetry to a portion of the amplifier 12, arranged at a central portion of the unit cell 30, occupying the pixel with respect to the center of the pixel. Therefore, the center of mass of the photoelectric conversion element 11 of the G pixel is at the center of the G pixel. With this configuration, intervals, D, of the photoelectric conversion elements  $q_{11}$  and  $q_{12}$  of G pixels become the same both in the row and column directions.

Further, a pixel covered by red filter (R pixel) is arranged in the upper right pixel in the unit cell 30, and a pixel covered by blue filter (B pixel) is arranged in the lower left pixel in the unit cell 30. These pixels do not have light-shield units, differing from the G pixels; however, since a single R pixel and a single B pixel are arranged in each unit cell 30, the intervals between adjacent R and B pixels become identical, namely 2D.

FIG. 22 is another layout of amplifiers 12 in pixels. In this layout, areas occupied by the amplifier 12 and the light-shield units 17 are reduced in the G pixels.

[Layout 1]

FIG. 23 shows a practical pattern layout of four photodiodes and an amplifier in the CMOS sensor 22 in FIG. 1.

The CMOS sensor, as shown in FIG. 23, is formed on a singlecrystalline silicon substrate based on a layout rule 0.4  $\mu$ m. Each pixel is a square, 8  $\mu$ m each side, and a source follower amplifier, as the amplifier 12, is shared by four pixels arranged in a 2×2 array. Therefore, the size of a unit

17

cell 481, shown by a dash line, is  $16 \mu m \times 16 \mu m$ . A plurality of unit cells 481 are arranged in two dimensions.

Photodiodes 482a, 482b, 482c, and 482d are formed diagonally in each pixel, and the shapes of the photodiodes **482***a* to **482***d* are nearly symmetry with respect to the center 5 of the unit cell 481 as well as symmetry with respect to vertical and horizontal lines passing over the center of the unit cell 481. Further, the center of mass (CM) of each photodiode is designed to be at the same position in each pixel. Further, reference numeral 495 denotes a light-shield 10

Reference numeral 488a is a scanning line for controlling a transfer gate 483a; 490, a row selection line; and 492, a reset line for controlling a gate 493 of a MOS transistor.

Photo-charges accumulated in the photodiodes 482a to 15 **482***d* are transferred to a floating diffusion (FD) portion **485** via transfer gates 483a to 483d, respectively. The size of the transfer gates 483a to 483d is L=0.4  $\mu$ m, W=1.0  $\mu$ m (L is a channel length and W is a channel width).

The FD portion 485 is connected to the gate 486 of a 20 source follower via an aluminum (Al) wire having a width of 0.4  $\mu$ m, and the photo-charge transferred to the FD portion 485 modulates the gate voltage of the gate 486. The size of the MOS transistor of the gate 486 is L= 0.8  $\mu$ m, W=1.0  $\mu$ m, and the total capacitance of the FD portion 485 25 and the gate 486 is about 5 fF. Since Q=CV, the gate voltage of the gate 486 changes by 3.2 volts in response to the transference of 10<sup>5</sup> electrons.

Current flowing in from a  $V_{DD}$  terminal 491 is modulated by the MOS transistor of the gate 486, and transferred to a 30 vertical signal line 487. Current flowing through the vertical signal line 487 is processed by a signal processing circuit (not shown) and formed into image information.

Thereafter, in order to set the potentials of the photodiodes **482***a* to **482***d*, the FD portion **485**, and the gate **486** to the 35 predetermined potential  $V_{DD}$ , the gate 486 of the MOS transistor connected to the reset line 482 is opened (at this time, the transfer gates 483a to 483d are also opened), thereby the photodiodes 482a to 482d, the FD portion 485, terminal 491.

Thereafter, the transfer gates 483a to 483d are closed, thereby the accumulation of photo-charges in the photodiodes 482a to 482d start again.

In layout 1, the lines 488a to 488d, 490 and 492, passing 45 over the unit cell 481 in the horizontal direction, are all formed with indium tin oxide, transparent conductor, of 1500 Å thickness. Therefore, areas of the photodiodes 482a to 482d under the aforesaid lines can also receive light, and the center of mass of each photodiode matches the center of 50 mass of light-receiving area of the photodiode.

According to the Layout 1 in the third embodiment, it is possible to provide a CMOS sensor with relatively high area ratio and high aperture ratio, in which photodiodes are arranged at an equal pitch.

[Layout 2]

FIG. 24 shows another practical pattern layout of four photodiodes and an amplifier in the CMOS sensor 22.

Referring to FIG. 24, reference numerals 502a to 502b denote the photodiodes; 503a to 503d, transfer gates; 505, an 60 FD portion; 506, the gate of a source follower; 507, a vertical signal line; 508a to 508d, scanning lines; 510, a row selection line; and 512, a reset line for controlling the gate **513** of a MOS transistor.

In layout 2 of the third embodiment, since three lines out 65 of lines 508a to 508d, 510, and 512 pass through the central portion of each pixel. Therefore, if these lines are metal

18

wires which shield light incoming toward the photodiodes 502a to 502d, the center of mass of the light-receiving area of each photodiode does not shift, and remains at the center of each pixel.

In layout 2 of the third embodiment, opaque metal wires with small resistance are generally used, time constant of the lines in the horizontal direction is improved, and a highspeed image sensing apparatus is obtained.

In the aforesaid layout 1 and layout 2 of the third embodiment, the portion under the shield unit is not effectively used. It is possible to extend the area of a photodiode, as a photoelectric conversion element, under the light-shield unit, and make the extended area function as a charge accumulation unit.

[Lavout 3]

In layout 2 of the third embodiment, since the lines pass through the center of each pixel where light-receiving efficiency is high, sensitivity of the image sensing apparatus may not be good. Accordingly, an improved layout is shown in FIG. 26 as the layout 3 of the third embodiment. FIG. 26 is a practical pattern layout of the layout shown in FIG. 20.

In layout 3 of the third embodiment, transfer gates 523a to 523d, the gate 526 of a source follower, and the gate 533 of a MOS transistor for resetting are formed under scanning lines 528a to 528d, a row selection line 530, and a reset line 532; therefore, it is possible to maximize the size and aperture of each of photodiodes 522a to 522d. In addition, the aperture of each photodiode is at the center of each pixel. Further, light-shield units are formed in an area where horizontal and vertical wires are formed.

Further, in layout 3 of the third embodiment, the source follower, as the amplifier 12 shown in FIG. 20, and the MOS transistor for resetting are separately arranged in periphery of each photodiode in the row direction, thus, compactly arranged under wires running in the row direction.

Further, since there is a large area which is not yet used under wires in the upper right pixel, it is possible to add a new configuration, such as a smart sensor.

According to the layout 3 of the third embodiment, the and the gate 486 are electrically connected to the  $V_{DD}$  40 area and aperture of a photodiode are increased comparing to the layout 2, it is possible to provide a high-sensitive image sensing apparatus with wide dynamic range. In addition, if the size of each pixel is further reduced and the size of the aperture of the photodiode becomes small, e.g., wavelength of light, each side, the problem such that light will not enter the photodiode will not arise. Thus, the layout 3 would remain as an efficient layout for the future.

> In layout 3 of the third embodiment, the amplifier 12 is arranged at the central portion of each unit cell, and the center of mass of a light-receiving area is designed to match the center of mass of a pixel. However, the present invention is not limited to this, and the shape of apertures of pixels may be arbitrarily designed as long as the shape is identical and arranged in a fixed position in every pixel, as shown in 55 FIG. 27, for instance.

In other words, by designing the apertures to have the same shape and arranged in a predetermined position in each pixel, intervals between the centers of mass of light receiving areas become the same.

[Layout 4]

FIG. 28 shows a practical pattern layout, corresponding to FIG. 21, of four photodiodes and an amplifier in the CMOS sensor 22 in FIG. 1.

In layout 4 of the third embodiment, colors of a color filter and positions of the colors are predetermined. Specifically, in the four pixels arranged in a 2×2 array, the upper left and lower right pixels are covered with green filter (G pixels)

19

which contributes most to luminance signals, the upper right pixel is covered with red filter (R pixel), and the lower left pixel is covered with blue filter (B pixel).

In layout 4, the amplifier 12 and other peripheral circuits are arranged so that photodiodes 542a and 542d of the G 5 pixels have the maximum area and aperture ratio.

Further, the center of mass of light-receiving area of a G pixel matches the center of mass of the G pixel, thus, the intervals between the centers of mass of G pixels are equal.

According to the layout 4 of the third embodiment, it is possible to provide a high sensitive image sensing apparatus.

[On-chip Lens and Other Variations]

FIG. 29 shows an example when on-chip lens is used in the CMOS sensor 22 in FIG. 1.

Referring to FIG. 29, an on-chip lens 602 is formed on each pixel in a unit cell 601. Light incoming from outside of the CMOS sensor 22 is collected by the on-chip lens 602 and incidents on the aperture 603. Reference numeral 604 denotes an imaging area where light is gathered by the on-chip lens 602.

By controlling the design and the position of the on-chip lens, the position of the imaging area can be set relatively freely.

Thus, when a plurality of pixels share a single amplifier, 25 if photodiodes, as photoelectric conversion elements, could not be arranged at a same interval, image signals as if they are obtained by photodiodes which are arranged at a same interval can be obtained by controlling the designs and positions of on-chip lenses.

Further, if an image sensing lens used in the image sensing apparatus is not telecentric, an incoming angle of light which incidents on a sensor chip in the central portion is different from an outer portion. Thus, by setting apertures of photodiodes in the outer portion of the CMOS sensor at 35 different intervals, image signals as if they are obtained by photodiodes which are arranged at a same interval can be obtained.

According to the layout 1 to layout 4 of the third embodiment, light-shield units which are optical members are 40 adjusted to make intervals between light-receiving areas identical. With the on-chip lens, the intervals of light receiving areas are made identical virtually by adjusting the designs and positions of the on-chip lenses, i.e., other optical members.

It should be noted that a configuration using an optical member, such as an on-chip lens, is also applicable to the first and second embodiments.

[Noise Reduction]

The inventors of the present application also have developed a signal read circuit for reducing noise suitably used in an image sensing apparatus having a configuration, as described above, in which a plurality of pixels share an amplifier.

FIG. 30 is a circuit diagram of a unit cell of the CMOS sensor having any of the aforesaid configurations.

Referring to FIG. 30, references  $q_{11}$ ,  $q_{12}$ ,  $q_{21}$ , and  $q_{22}$  are photodiodes as photoelectric conversion elements;  $M_{TX1}$  to  $M_{TX4}$ , MOS transistors for transferring photo-charges accumulated in the photodiodes  $q_{11}$ ,  $q_{12}$ ,  $q_{21}$ , and  $q_{22}$  to a floating diffusion (FD) portion;  $M_{RES}$ ; a MOS transistor for resetting the FD portion; and  $M_{SF}$  and  $M_{SEL}$ , MOS transistors configuring a source follower. The MOS transistor  $M_{SEL}$  also functions as a selection switch for selecting a photodiode.

Next, an operation of the image sensing apparatus including a signal processing circuit according to the third embodi20

ment is explained. FIG. 31 is an equivalent circuit of the image sensing apparatus including the signal processing unit

FIG. 32 is a timing chart for operating the image sensing apparatus shown in FIG. 31.

Referring to FIGS. 31 and 32, vertical scanning operation is initiated in response to the pulse, which indicates a vertical blanking period, of a signal  $\phi V_1$  or  $\phi V_2$ . First, a signal  $\phi TX_{RO}$  which is applied to a reset line 573 of the first row is activated during a horizontal blanking period (i.e., when a signal  $\phi HBL$  is high), and signals for subsequent lines are applied in the same manner. Accordingly, all the pixels in every row are reset to the reset potential  $V_{DD}$ .

In each horizontal blanking period, as shown in FIG. 32, during a period  $T_{11}$ , a signal  $\phi$ L becomes high and a transistor 561, connected for a vertical signal line 557, is turned on and the vertical signal line 557 is reset. Simultaneously, signals  $\phi$ T<sub>N</sub>,  $\phi$ T<sub>S1</sub> and  $\phi$ T<sub>S2</sub> also become high, and transistors 562-1 to 562-3 are turned on. Accordingly wires in the upstream of transistors for reading signal, 564-1 to 564-3, and capacitors 563-1 to 563-3 (C<sub>TN</sub>, C<sub>TS1</sub>, C<sub>TS2</sub>) are electrically connected to the vertical signal line 557, and reset. Accordingly, residual charges in the capacitors 563-1 to 563-3, for instance, are removed.

Thereafter, in a period  $T_{12}$ , a signal  $\phi TX_{RO}$  to be applied to the reset line **573** is changed to high, and the floating gate, which is the gate of the source follower amplifier configured with the MOS transistors  $M_{SF}$  and  $M_{SEL}$  in each unit cell, is reset to the voltage  $V_{DD}$ .

Then, in a period  $T_{13}$ , a signal  $\phi RV$  becomes high and a transistor **560** for grounding, connected to the vertical signal line **557**, is turned on, and the vertical signal line **557** is grounded. Simultaneously, the signal  $\phi T_N$  is changed to high in order to connect the capacitor **563-1** ( $C_{TN}$ ) for storing a noise component to the vertical signal line **557**, and the transistor **562-1** is turned on. At this time, a signal  $\phi S_O$  to be applied to a row selection line **574** is high, and current corresponding to the potential (about  $V_{DD}$ ) at the floating gate of the MOS transistor  $M_{SF}$  flows from a  $V_{DD}$  terminal to the capacitor **563-1** ( $C_{SF}$ ) thereby the capacitor **563-1** ( $C_{TN}$ ) stores charge corresponding to the noise component.

Next, in a period T<sub>14</sub>, a signal φTX<sub>OOO</sub> applied to the odd-column scanning line **571** is changed to high, in turn, a transfer gate (MOS transistor M<sub>TX1</sub>, in this case) for an odd-number column in an odd-number row is turned on, and photo-charge accumulated in the photodiode q<sub>11</sub> is transferred to the floating gate of the MOS transistor M<sub>SF</sub>. The capacitor **563-1** (C<sub>TN</sub>) for storing the noise component is disconnected from the vertical signal line **557** when the signal φT<sub>N</sub> becomes low, and the capacitor **563-2** (C<sub>TS1</sub>) for storing a photo-charge signal is connected, in turn, when the signal φT<sub>S1</sub> is changed to high. Thus, charge accumulated in the photodiode q<sub>11</sub>, for instance, in an odd-number column in an odd-number row is stored in the capacitor **563-2** (C<sub>TS1</sub>) via the vertical signal line **557**.

Next, in a period  $T_{1S1}$  the signal  $\phi L$  becomes high, and only the vertical signal line **557** is reset. Since the signals  $\phi S_O$ ,  $\phi T_N$ ,  $\phi T_{S1}$ , and  $\phi T_{S2}$ , are low, other portions are not reset, and their states are preserved.

Next, the signal  $\phi TX_{RO}$  applied to the reset line **573** is changed to high between periods  $T_{15}$  and  $T_{16}$ , and the gate of the source follower amplifier (i.e., the gate of MOS transistor  $M_{SF}$ ) is reset to the potential  $V_{DD}$ .

In the period  $T_{16}$ , a signal  $\phi TX_{OeO}$  applied to a scanning 65 line 572 is changed to high, and photo-charge accumulated in the photodiode  $q_{12}$  in an even-number column in an odd-number row is transferred to the floating gate of the

21

MOS transistor  $M_{SF}$ . At this time, the signal  $\phi T_{S2}$  is changed to high, and photo-charge accumulated in the photodiode  $P_{12}$  is stored in the capacitor **563-3** ( $C_{TS2}$ ) via the vertical signal line **557**, in the similar manner.

In the aforesaid manner, charges corresponding to the 5 noise component, a first signal, and a second signal are respectively stored in the capacitors 563-1, 563-2, and 563-3 ( $C_{TN}$ ,  $C_{TS1}$ ,  $C_{TS2}$ ) by each column for a row.

Next, in a period T<sub>17</sub>, in order to sequentially transfer the charges stored in the capacitors 563-1 to 563-3 ( $C_{TN}$ ,  $C_{TS1}$ ,  $C_{TS2}$ ) to amplifiers 566-1 to 566-3, respectively, a horizontal scanning signal  $\phi$ Hn is changed to high for each columns controlled by a horizontal shift register 559, and transistors 564-1 to 564-3, provided for each column, are turned on; thereby the capacitors 563-1 to 563-3 ( $C_{TN}$ ,  $C_{TS1}$ ,  $C_{TS2}$ ) are 15 connected to the respective amplifiers 566-1 to 566-3. From the capacitors 563-1 to 563-3 ( $C_{TN}$ ,  $C_{TS1}$ ,  $C_{TS2}$ ), the noise component, the first signal, and the second signal are outputted, and from a differential amplifier 567-1, a signal S1 obtained by subtracting the noise component from the first 20 signal is outputted, and a signal S2 obtained by subtracting the noise component from the second signal is outputted from a differential amplifier 567-2. Note that accumulation of photo-charges by the photodiodes are also performed during the period  $T_{17}$ .

Further, by changing signals  $\phi TX_{OOe}$  and  $\phi TX_{Oee}$  to high instead of the signals  $\phi TX_{OOO}$  and  $\phi TX_{OeO}$  in the aforesaid operation, signals corresponding to photo-charges accumulated in the photodiodes  $q_{21}$  and  $q_{22}$  in an even-number row are read out and a noise component is subtracted from those 30 photo-charge signals to obtain the signals S1 and S2.

#### First Modification of the Third Embodiment

Next, another configuration of an image sensing apparatus 35 including a signal processing circuit is explained.

FIG. 33 is an equivalent circuit of the image sensing apparatus including the signal processing unit.