| Case 1:16-cv-00290-MN | Document 1-18 | Filed 04/22/16 | Page 1 of 5 PageID #: 349   |

|-----------------------|---------------|----------------|-----------------------------|

|                       |               |                | . a.g. = 0. 0 . a.g. = 0 .0 |

# **EXHIBIT R**

### Case 1:163-19780002901181017, 2005220011eOth Initials in the coast 2016 in Rage 8858 (P. Prage 1) #: 350

| 1  |   |               | 1 .     |             |

|----|---|---------------|---------|-------------|

|    | Δ | semiconductor | device  | comprising. |

| 1, |   | semiconductor | ucvicc, | comprising. |

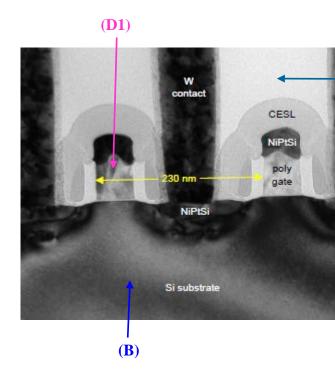

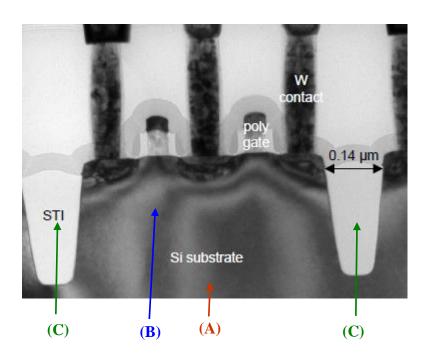

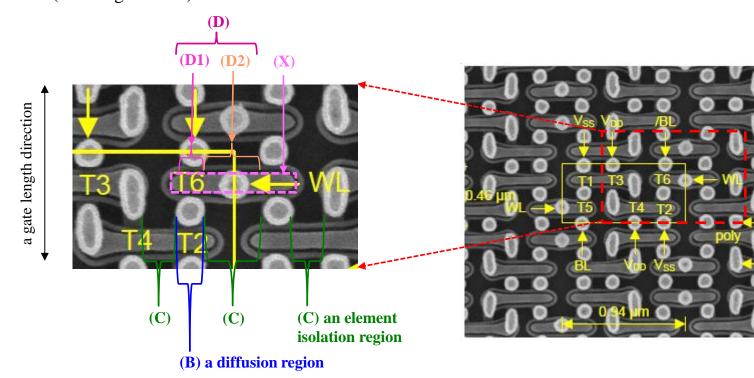

- (A) a semiconductor substrate;

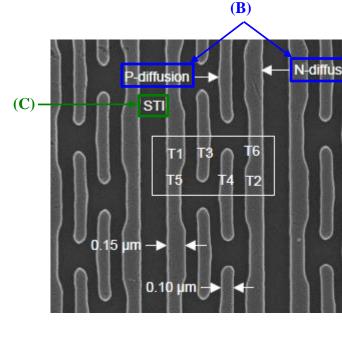

- (B) a diffusion region which is formed in the semiconductor substrate and serves as a region for the formation of a MIS (C) an element isolation region surrounding the diffusion region;

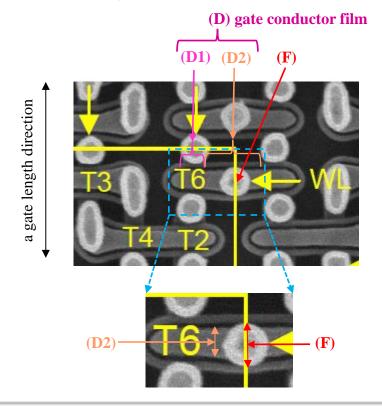

- at least one **(D)** gate conductor film which is formed across the diffusion region and the element isolation region, inclugate electrode part located on the diffusion region and **(D2)** a gate interconnect part located on the element isolation has **(X)** a constant dimension in a gate length direction;

- (E) an interlayer insulating film covering (D1) the gate electrode part; and

- (F) a gate contact which passes through the (E) interlayer insulating film, is connected to (D2) the gate interconnect a dimension in the gate length direction larger than (D2) the gate interconnect part.

## Case 1: <u>frantyb002901NdN 7, 279972771eOtn1mix3sidTilred: 0A/R2/126 InRagrev 88.58 (Fragrel D</u> #: 351

#### Claim 1

A semiconductor device, comprising: (A) a semiconductor substrate; (B) a diffusion region which is formed in the se substrate and serves as a region for the formation of a MIS transistor; (C) an element isolation region surrounding the region;

(Cross section: gate length direction)

(Plane : diffusion level)

## Case 1: <u>frantyb002901MtN 7, 279072771eOtn1mix3sidTilted: 0A/R2/126 InRagrev8858 & Pragrel P</u> #: 352

Claim 1

at least one **(D)** gate conductor film which is formed across the diffusion region and the element isolation region, inclugate electrode part located on the diffusion region and **(D2)** a gate interconnect part located on the element isolation has **(X)** a constant dimension in a gate length direction;

(Plane: gate level)

## Case 1: <u>francos 10290 (NAN 7, 200) (2000) (NAN 7, 200) (2000) (NAN 7, 200) (2000) (NAN 7, 200) </u>

Claim 1

(E) an interlayer insulating film covering (D1) the gate electrode part; and (F) a gate contact which passes through the (E) interlayer insulating film, is connected to (D2) the gate interconnect a dimension in the gate length direction larger than (D2) the gate interconnect part.

(Plane: gate level)

(Cross section: gate length direction)