Case 1:14-cv-01430-CJB Document 521-1 Filed 06/06/22 Page 1 of 46 PageID #: 28702

# EXHIBIT 1

US008907499B2

## (12) United States Patent

### Leedy

#### (54) THREE DIMENSIONAL STRUCTURE MEMORY

- (71) Applicant: Glenn J Leedy, Carmel, CA (US)

- (72) Inventor: Glenn J Leedy, Carmel, CA (US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

This patent is subject to a terminal disclaimer.

- (21) Appl. No.: 13/734,874

- (22) Filed: Jan. 4, 2013

#### (65) **Prior Publication Data**

US 2013/0187290 A1 Jul. 25, 2013

#### **Related U.S. Application Data**

- (60) Continuation of application No. 12/788,618, filed on May 27, 2010, which is a continuation of application No. 10/143,200, filed on May 13, 2002, now abandoned, which is a continuation of application No. 09/607,363, filed on Jun. 30, 2000, now Pat. No. 6,632,706, which is a continuation of application No. 08/971,565, filed on Nov. 17, 1997, now Pat. No. 6,133,640, which is a division of application No. 08/835,190, filed on Apr. 4, 1997, now Pat. No. 5,915,167.

- (51) Int. Cl.

| H01L 23/48  | (2006.01) |

|-------------|-----------|

| G11C 5/02   | (2006.01) |

| H01L 25/065 | (2006.01) |

| H01L 27/06  | (2006.01) |

| H01L 21/768 | (2006.01) |

| H01L 23/522 | (2006.01) |

| H01L 27/108 | (2006.01) |

| G11C 5/06   | (2006.01) |

### (10) Patent No.: US 8,907,499 B2

### (45) **Date of Patent:** \*Dec. 9, 2014

#### (2013.01); H01L 23/5226 (2013.01); H01L 27/10897 (2013.01); H01L 23/481 (2013.01); G11C 5/06 (2013.01)

- USPC ...... **257/777**; 257/778; 257/685; 438/977

#### (56) **References Cited**

#### U.S. PATENT DOCUMENTS

| 2,915,722 A | 12/1959     | Foster  |

|-------------|-------------|---------|

| 3,202,948 A | 8/1965      | Farrand |

|             | (Continued) |         |

FOREIGN PATENT DOCUMENTS

| DE | 3233195 | 3/1983 |

|----|---------|--------|

| EP | 189976  | 8/1986 |

(Continued)

#### OTHER PUBLICATIONS

Bollmann et al., Three Dimensional Metallization for Vertically Integrated Circuits, MAM'97—Materials for Advanced Metallization.

(Continued)

Primary Examiner — David Lam

(74) Attorney, Agent, or Firm - Useful Arts IP

#### (57) ABSTRACT

A Three-Dimensional Structure (3DS) Memory allows for physical separation of the memory circuits and the control logic circuit onto different layers such that each layer may be separately optimized. One control logic circuit suffices for several memory circuits, reducing cost. Fabrication of 3DS memory involves thinning of the memory circuit to less than 50 microns in thickness and bonding the circuit to a circuit stack while still in wafer substrate form. Fine-grain high density inter-layer vertical bus connections are used. The 3DS memory manufacturing method enables several performance and physical size efficiencies, and is implemented with established semiconductor processing techniques.

#### 165 Claims, 9 Drawing Sheets

US 8,907,499 B2

5

20

or a conventional die), or a pattern for conventional insertion interconnect, DCA (Direct Chip Attach) or FCA (Flip-Chip Attach). If another circuit layer is to be bonded to the 3DScircuit stack, steps 1 through 4 are repeated.

6. Perform step 5A or 5B of Method A.

3DS Memory Device Yield Enhancement Methods

The 3DS circuit may be considered a vertically assembled MCM (Multi-Chip Module) and as with an MCM the final yield is the product of the yield probabilities of each component circuit (layer) in the completed 3DS circuit. The 3DS 10 circuit uses several yield enhancement methods that are synergistic in their combined usage within a single memory IC. The yield enhancement methods used in the 3DS memory circuit include small memory array block size, memory array block electrical isolation through physically unique or sepa- 15 rate vertical bus interconnections, intra memory array block gate-line sparing, memory array layer sparing (inter-block gate-line sparing), controller sparing and ECC (Error Correcting Codes). The term sparing is used to mean substitution by a redundant element.

The selected size of the memory array block is the first component in the yield equation for the 3DS memory circuit. Each memory array block is individually (uniquely) accessed and powered by the controller circuit and is physically independent of each and every other memory array block includ- 25 ing those on the same memory array layer in addition to those on a different memory array layer. The size of the memory array block is typically less than 5 mm<sup>2</sup> and preferably less than 3 mm<sup>2</sup>, but is not limited to a specific size. The size of memory array block, the simplicity of its NMOS or PMOS 30 fabrication process and its physical independence from each of the other memory array blocks, for nearly all production IC processes, provides a conservatively stated nominal yield of greater than 99.5%. This yield assumes that most point defects in the memory array block such as open or shorted 35 interconnect lines or failed memory cells can be spared (replaced) from the intra-block or inter-block set of redundant gate-lines. Major defects in a memory array block which render the complete memory array block unusable result in the complete sparing of the block from a redundant memory 40 array layer or the rejection of the 3DS circuit.

In the example of a 3DS DRAM circuit the yield of a stack of memory array blocks is calculated from the yield equation Ys = ((1 - (1 - PY)2)n)b, where n is the number DRAM array layers, b is the number of blocks per DRAM array and Py is 45 the effective yield (probability) of a DRAM array block less than 3 mm2 in area. Assuming a DRAM array block redundancy of 4% for gate-lines in the DRAM array block lines and one redundant DRAM array layer, and assuming further that the number of blocks per layer is 64, the number of memory 50 array layers in the stack is 17 and the effective value for Py is 0.995, then the stack yield Ys for the complete memory array (including all memory array block stacks) is 97.47%.

The Ys memory array stack yield is then multiplied by the yield of the controller Yc. Assuming a die size of less than 50 55 mm<sup>2</sup>, a reasonable Yc for a controller fabricated from a 0.5 micron BiCMOS or mixed signal process would be between 65% and 85%, giving a net 3DS memory circuit yield of between 63.4% and 82.8%. If a redundant controller circuit layer is added to the 3DS memory stack, the yield probabili- 60 ties would be between 85.7% and 95.2%.

The effective yield of a memory array block can be further increased by the optional use of ECC logic. ECC logic corrects data bit errors for some group size of data bits. The syndrome bits necessary for the operation of ECC logic 65

necessary, in order to accommodate the storage of ECC syndrome bits, additional memory array layers could be added to the circuit.

Advantageous 3DS Memory Device Controller Capabilities As compared to a conventional memory circuit, the 3DS memory controller circuit can have various advantageous capabilities due the additional area available for controller circuitry and the availability of various mixed signal process fabrication technologies. Some of these capabilities are selftest of memory cells with dynamic gate-line address assignment, virtual address translation, programmable address windowing or mapping, ECC, data compression and multi-level storage.

Dynamic gate-line address assignment is the use of programmable gates to enable the layer and gate-line for a read/ write operation. This allows the physical order of memory storage to be separate or different from the logical order of stored memory.

The testing of each generation of memory devices has resulted in significantly increased test costs. The 3DS memory controller reduces the cost of testing by incorporating sufficient control logic to perform an internal test (selftest) of the various memory array blocks. Circuit testing in the conventional ATE manner is required only for verification of controller circuit functions. The scope of the internal test is further extended to the programmable (dynamic) assignment of unique addresses corresponding to the various gate-lines of each memory array block on each layer. Self-test capability of the 3DS controller circuit can be used anytime during the life of the 3DS memory circuit as a diagnostic tool and as a means to increase circuit reliability by reconfiguring (sparing) the addresses of gate-lines that fail after the 3DS memory circuit is in use in a product.

ECC is a circuit capability that, if included in the controller circuit, can be enabled or disabled by a programming signal or made a dedicated function.

Data compression logic will allow the total amount of data that can be stored in the 3DS memory array to be increased. There are various generally known data compression methods available for this purpose.

Larger sense amps allow greater dynamic performance and enable higher speed read operations from the memory cells. Larger sense amps are expected to provide the capability to store more than one bit (multi-level storage) of information in each memory cell; this capability has already been demonstrated in non-volatile memory circuits such as flash EPROM. Multi-level storage has also been proposed for use in the 4 Gbit DRAM generation circuits.

It will be appreciated by those of ordinary skill in the art that the invention can be embodied in other specific forms without departing from the spirit or essential character thereof. The presently disclosed embodiments are therefore considered in all respects to be illustrative and not restrictive. The scope of the invention is indicated by the appended claims rather than the foregoing description, and all changes which come within the meaning and range of equivalents thereof are intended to be embraced therein.

#### The invention claimed is:

1. A thin and substantially flexible structure comprising: a thin, substantially flexible monocrystalline semiconduc-

tor layer of one piece; and

a silicon-based dielectric layer formed on the thin semi-

Find authenticated court documents without watermarks at docketalarm.com

#### US 8,907,499 B2

**2**. The thin and substantially flexible structure of claim **1**, further comprising:

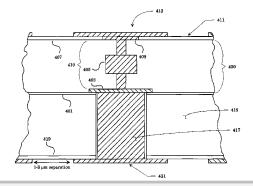

- a vertical interconnect conductor extending vertically through the thin semiconductor layer; and

- a vertical silicon-based dielectric insulator extending ver- $^{5}$  tically through the thin semiconductor layer and around the interconnect conductor and having a stress of less than  $5 \times 10^{8}$  dynes/cm<sup>2</sup> tensile.

**3**. The thin and substantially flexible structure of claim **2**, wherein:

- the thin semiconductor layer comprises vertical holes etched therethrough; and

- the vertical interconnect conductor and the vertical siliconbased dielectric insulator are formed in one of the vertical holes of the thin semiconductor layer.

**4**. The thin and substantially flexible structure of claim **2**, wherein the thin semiconductor layer is formed from a semiconductor wafer.

5. The thin and substantially flexible structure of claim 2,  $_{20}$  wherein the thin semiconductor layer has a thickness of 50 microns or less.

**6**. The thin and substantially flexible structure of claim **4**, wherein the semiconductor wafer comprises monocrystalline silicon, and the thin semiconductor layer comprises monoc- 25 rystalline silicon formed from the semiconductor wafer.

7. The thin and substantially flexible structure of claim 2, wherein the thin semiconductor layer is unitary.

**8**. The thin and substantially flexible structure of claim **2**, wherein the thin semiconductor layer extends from edge to 30 edge of the dielectric layer.

**9**. The thin and substantially flexible structure of claim **8**, wherein the dielectric layer extends from edge to edge of the thin semiconductor layer.

**10**. The thin and substantially flexible structure of claim **1**, 35 wherein the thin semiconductor layer comprises a polished surface formed by removing semiconductor material during thinning of the thin semiconductor layer to expose a surface thereof and then polishing the exposed surface, wherein the thin semiconductor layer is substantially flexible based on 40 being thinned and having the polished surface.

**11**. The thin and substantially flexible structure of claim **2**, further comprising:

a bottomside surface and a topside surface;

- a contact formed on the bottomside surface and electrically 45 connected to the vertical interconnect conductor; and

- an interconnect, contact or circuit formed on or near the topside surface and electrically connected to the vertical interconnect conductor;

- wherein the interconnect, contact or circuit is electrically 50 connected to the contact on the bottomside surface via the vertical interconnect.

- 12. A thin and substantially flexible circuit comprising:

a thin monocrystalline semiconductor layer of one piece;

- a silicon-based dielectric layer formed on the thin semiconductor layer and having a stress of less than  $5 \times 10^8$  dynes/cm<sup>2</sup> tensile; and

- circuitry supported by the thin semiconductor layer and the dielectric layer defining an integrated circuit die having an area, wherein the thin semiconductor layer extends 60 throughout a substantial portion of the area of the integrated circuit die.

13. The thin and substantially flexible circuit of claim 12, comprising:

a vertical interconnect conductor extending vertically 65

a vertical silicon-based dielectric insulator extending vertically through the thin semiconductor layer and around the interconnect conductor and having a stress of less than  $5 \times 10^8$  dynes/cm<sup>2</sup> tensile.

14. The thin and substantially flexible circuit of claim 13, wherein the thin semiconductor layer is formed from a semiconductor wafer.

**15**. The thin and substantially flexible circuit of claim **13**, wherein the thin semiconductor layer has a thickness of 50 10 microns or less.

**16**. The thin and substantially flexible circuit of claim **14**, wherein the semiconductor wafer comprises monocrystalline silicon, and the thin semiconductor layer comprises monocrystalline silicon formed from the semiconductor wafer.

17. The thin and substantially flexible circuit of claim 13, wherein the thin semiconductor layer is unitary.

**18**. The thin and substantially flexible circuit of claim **13**, wherein the thin semiconductor layer extends from edge to edge of the dielectric layer.

**19**. The thin and substantially flexible circuit of claim **18**, wherein the dielectric layer extends from edge to edge of the thin semiconductor layer.

**20**. The thin and substantially flexible circuit of claim **12**, wherein the thin semiconductor layer comprises a polished surface formed by removing semiconductor material during thinning of the thin semiconductor layer to expose a surface thereof and then polishing the exposed surface, wherein the thin semiconductor layer is substantially flexible based on being thinned and having the polished surface.

**21**. The thin and substantially flexible circuit of claim **13**, further comprising:

a bottomside surface and a topside surface;

a contact formed on the bottomside surface and electrically connected to the vertical interconnect conductor; and

- an interconnect, contact or circuit formed on or near the topside surface and electrically connected to the vertical interconnect conductor;

- wherein the interconnect, contact or circuit is electrically connected to the contact on the bottomside surface via the vertical interconnect.

- 22. A structure comprising:

a monocrystalline semiconductor layer of one piece; and

- a silicon-based dielectric layer formed on the semiconductor layer and having a stress of less than 5×10<sup>8</sup> dynes/ cm<sup>2</sup> tensile;

- wherein the semiconductor layer is capable of being thinned to obtain a thin and substantially flexible substrate.

23. The structure of claim 22, comprising:

- a vertical interconnect conductor extending vertically through the thin semiconductor layer and coupled to said circuitry; and

- a vertical silicon-based dielectric insulator extending vertically through the thin semiconductor layer and around the interconnect conductor and having a stress of less than  $5 \times 10^8$  dynes/cm<sup>2</sup> tensile.

**24**. A thin and substantially flexible integrated circuit comprising:

- a thin, substantially flexible monocrystalline semiconductor layer of one piece comprising integrated circuit devices; and

- a silicon-based dielectric layer formed on the thin semiconductor layer and having a stress of less than  $5 \times 10^8$  dynes/cm<sup>2</sup> tensile.

- 25. The structure of claim 23, wherein:

Case 1:14-cv-01430-CJB Document 521-1 Filed 06/06/22 Page 5 of 46 PageID #: 28706

# EXHIBIT 2

# DOCKET A L A R M

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time alerts** and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

## API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

## LAW FIRMS

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

## FINANCIAL INSTITUTIONS

Litigation and bankruptcy checks for companies and debtors.

## E-DISCOVERY AND LEGAL VENDORS

Sync your system to PACER to automate legal marketing.