## EXHIBIT 7

### (12) United States Patent Konda

#### (54) OPTIMIZATION OF MULTI-STAGE HIERARCHICAL NETWORKS FOR PRACTICAL ROUTING APPLICATIONS

(71) Applicant: Venkat Konda, San Jose, CA (US)

Inventor: Venkat Konda, San Jose, CA (US)

Assignee: Konda Technologies Inc., San Jose,

CA (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 107 days.

This patent is subject to a terminal dis-

claimer.

Appl. No.: 15/140,470

Apr. 28, 2016 (22)Filed:

(65)**Prior Publication Data**

> US 2016/0261525 A1 Sep. 8, 2016

(51) Int. Cl.

H04L 12/933 (2013.01)H04L 29/06

(2006.01)

(52) U.S. Cl.

CPC .... H04L 49/1515 (2013.01); H04L 29/06081 (2013.01); H04L 49/109 (2013.01); H04L

65/4076 (2013.01)

(58) Field of Classification Search

CPC ...... H04L 49/1515; H04L 65/4076; H04L 29/06081

See application file for complete search history.

#### (56)**References Cited**

#### U.S. PATENT DOCUMENTS

5,153,843 A 10/1992 Batcher 5,345,444 A \* 9/1994 Cloonan ...... H04L 12/5601 370/381

#### US 10,003,553 B2 (10) Patent No.:

#### (45) **Date of Patent:**

\*Jun. 19, 2018

9/1995 Yang et al. 5,451,936 A 5,541,914 A 7/1996 Krishnamoorthy ... H04L 49/254 5,654,695 A \* 8/1997 Olnowich .......... G06F 13/4022 340/2.23

6,018,523 A 1/2000 Even 7/2000 Even ...... H04L 49/1507 6,091,723 A \* 340/2.21

6,185,220 B1 2/2001 Muthukrishnan et al.

(Continued)

#### OTHER PUBLICATIONS

Ronald I. Greenberg, "The Fat-Pyramid and Universal Parallel Computation Independent of wire delay" IEEE Trans. Computers, 43(12):1358-1364, Dec. 1994.

(Continued)

Primary Examiner — Rasheed Gidado

#### (57)**ABSTRACT**

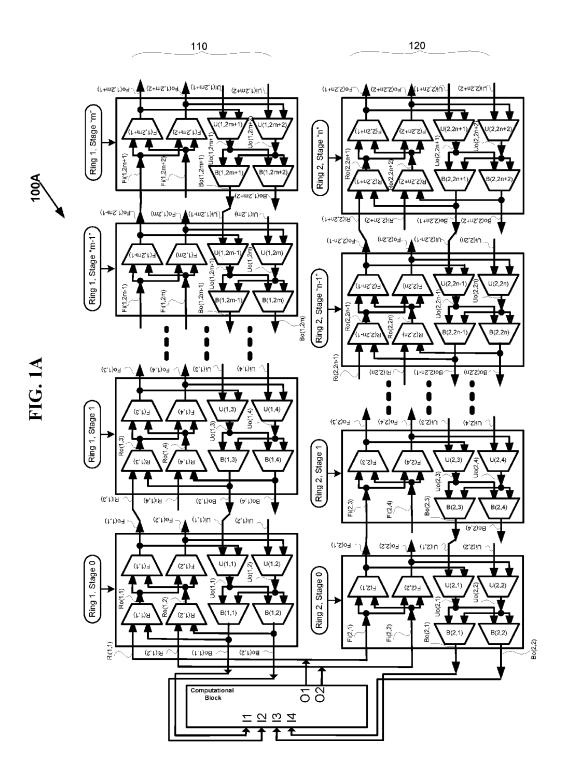

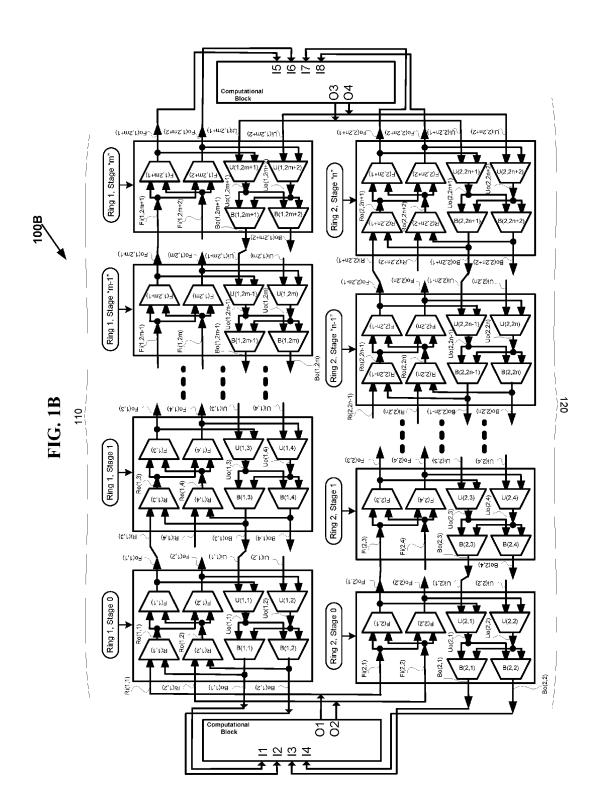

Significantly optimized multi-stage networks, useful in wide target applications, with VLSI layouts using only horizontal and vertical links to route large scale sub-integrated circuit blocks having inlet and outlet links, and laid out in an integrated circuit device in a two-dimensional grid arrangement of blocks are presented. The optimized multi-stage networks in each block employ several rings of stages of switches with inlet and outlet links of sub-integrated circuit blocks connecting to rings from either left-hand side only, or from right-hand side only, or from both left-hand side and right-hand side; and employ shuffle exchange links where outlet links of cross links from switches in a stage of a ring in one sub-integrated circuit block are connected to either inlet links of switches in the another stage of a ring in the same or another sub-integrated circuit block.

#### 20 Claims, 19 Drawing Sheets

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 6,335,930    | B1*  | 1/2002  | Lee H04L 49/101                 |

|--------------|------|---------|---------------------------------|

| 6,469,540    | B2 * | 10/2002 | 370/387<br>Nakaya H03K 19/17728 |

|              |      |         | 326/38                          |

| 6,940,308    | B2   | 9/2005  | Wong                            |

| 7,440,449    | B2 * | 10/2008 | Carson G06T 7/20                |

|              |      |         | 257/499                         |

| 8,170,040    | B2   | 5/2012  | Konda                           |

| 8,269,523    | B2   | 9/2012  | Konda                           |

| 8,270,400    | B2   | 9/2012  | Konda                           |

| 8,363,649    | B2   | 1/2013  | Konda                           |

| 8,898,611    | B2   | 11/2014 | Konda                           |

| 9,374,322    | B2   | 6/2016  | Konda                           |

| 9,529,958    | B2   | 12/2016 | Konda                           |

| 2003/0117946 | A1*  | 6/2003  | Fontana H04L 12/437             |

|              |      |         | 370/216                         |

| 2011/0037498 | A1*  | 2/2011  | Konda G06F 17/5077              |

|              | _    |         | 326/41                          |

| 2012/0269190 | A1*  | 10/2012 | Konda G06F 17/5054              |

| 2012 0209190 |      | 10.2012 | 370/388                         |

|              |      |         | 3/0/300                         |

#### OTHER PUBLICATIONS

Hypertree: A Multiprocessor Interconnection Topology , by James R. Goodman and Carlo H Sequin, Computer Science Technical Report #427, Dept , of EECS, University of California.

Data Movement Techniques for the pyramid computer, Russ Miller and Quentin F. Stout, SIAM Journal on Computing, vol. 16, No. 1, pp. 38-60, Feb. 1987.

C. Clos, "A Study of Non-Blocking Switching Networks," Bell System Technical Journal, 32:406-424, 1953.

A. DeHon, "Balancing Interconnect and Computation in a Reconfigurable Computing Array," ACM Int. Symp. on FPGA, pp. 69-78, Feb. 1999.

Chihming Chang, Rami Melhem, "Arbitrary Size Benes Networks", Journal: Parallel Processing Letters—PPL, vol. 7, No. 3, pp. 279-284, 1997.

Hoda El-Sayed and Abdou Youssef; "The r-truncated Benes Networks and their Randomized Routing Algorithms" 1997 Intl Conf on Parallel and Dist Sys. Seoul, Korea, Dec. 1997.

Guy Lemieux and David Lewis, "Using Sparse Crossbars within LUT Clusters", Procds of the ACM/SIGDA Intl Symp on Field Prog Gate Arrays 2001, Feb. 11-13, 2001, Monterey, CA.

P. Manuel, W. K. Qureshi, A. William, A. Muthumalai, "VLSI layout of Benes networks,", J. of Discrete Math. Sci. & Cryptography, vol. 10, No. 4, pp. 461-472, 2007.

Quinn, Michael J, "Parallel Computing: Theory and Practice", 2nd. ed., 1994, McGraw Hill Series in computer Science, Networks, and parallel computing, ISBN 0-07-051294-9.

A. DeHon, 'Unifying Mesh- and Tree-Based Programmable Interconnect,' IEEE Trans. on Very Large Scale Int. Systems, vol. 12, No. 10, pp. 1051-1065, Oct. 2004.

Guy Lemieux and David Lewis. Analtyical framework for switch block design. In Int'/. Conference on Field Programmable Logic and Applications, pp. 122-131, Sep. 2002.

Chen, G; Lau, FCM, "A tight layout of the cube-connected cycles", The 4th International Conference on High Perf. Computing, Bangalore, India, Dec. 18-21, 1997, p. 422-427.

Michael Shyu, Yu-Dong Chang, Guang-Ming Wu, and Yao-Wen Chang, Generic universal switch blocks. IEEE Transactions on Computers, 49(4):348-359, Apr. 2000.

Y. Yamada, et. al., "Folded Fat H-Tree: an interconnection topology for Dynamically Reconfigurable Processor Array", Embed and Ubiq. Cmpting, Intl Conf. EUC 2004.

A. DeHon. Balancing Interconnect and Computation in a Reconfigurable Computing Array (or, why you don't really want 100% LUT utili). In Proc. of intl. symp. on FPGAs, Feb. 1999. André DeHon. Compact, Multilayer Layout for Butterfly Fat-Tree. In Twelfth Annual ACM Symposium on Parallel Algs and Archi-

tectures (SPAA 2000), pp. 206-215, Jul. 9-12, 2000. V. P. Roychdowdhury et. al., "Segmented Channel Routing," IEEE Trans on Computer-Aided Design of Integrated Circuits and Sys-

tems, vol. 12, No. 1, pp. 79-95, Jan. 1993. Ivo Dobbelaere, Mark Horowitz, and Abbas El Gamal. Regenerative feedback repeaters for programmable interconnections. IEEE Journal of Solid-State Circuits, 30(11), 1995.

F. Petrini et. al., k-ary n-trees: High performance networks for massively parallel architectures, in: Proceedings of the 11th Intl Parallel Proc. Symp., IPPS'97, pp. 87-93.

P.Pande et al. "Evaluation of MP-SoC Interconnect Architectures: a Case Study", Proceedings of 4th IWSOC, Banff, Alberta, Canada, Jul. 19-21, 2004.

Yeh, C.-H., Varvarigos, E.A., Parhami, B.: Multilayer VLSI layout for interconnection networks. In: Proc. Intl. Conf. on Parallel Processing, 2000.

M. Lin, A. El Gamal, "A Low-Power Field-Programmable Gate Array Routing Fabric," IEEE Transactions on Very Large Scale Integration, vol. 17, No. 10, pp. 1481-1494, Oct. 2009.

Avior, A et. al., A Tight Layout of the Butterfly Network. Proc. 8-th Annual ACM Symp. on Parallel Alg. and Arch. (SPAA '96), ACM Press Ed., 1996, pp. 170-175.

A. El Gamal et. al., "An Architecture for Electrically Configurable Gate Arrays," IEEE Jrnl of Solid-State Circuits, vol. 24, No. 2, pp. 394-398, Apr. 1989.

Vaughn Betz et. al., Directional bias and non-uniformity in FPGA global routing architectures. In IEEE/ACM Intl. Conference on Computer-Aided Design, pp. 652-659, san jose, 96.

W. Tsu et. al., "HSRA: High-Speed, Hierarchical Synchronous Reconfigurable Array," in Procds. of the Intl. Symp. on Field-Programmable Gate Arrays, Feb. 1999, pp. 125-134.

André DeHon. Rent's Rule Based Switching Requirements. In System-Level Interconnect Prediction (SLIP 2001), pp. 197-204, Mar. 31-Apr. 1, 2001.

Guy Lemieux et.al., Generating highlyroutablesparse crossbars for PLDs. In ACMISIGDA Int'l. Symposium on Field Programmable Gate Arrays, pp. 155-164, Monterey, CA, Feb. 2000.

S. Sivaswamy et. al., "HARP: hard-wired routing pattern FPGAs", FPGA'05, Monterey, California, USA, Feb. 20-22, 2005.

Yeh, C.-H., E.A. Varvarigos, and B. Parhami, "Efficient VLSI layouts of hypercubic networks," Proc. Symp. Frontiers of Massively Parallel Computation, Feb. 1999.

Bhatt, S. N. and Leighton, F. T. 1984. A framework for solving VLSI graph layout problems. J. Comput. Syst. Sci. 28, 300-343.

\* cited by examiner

# DOCKET

## Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

#### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

### **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.