## EXHIBIT 4

US008269523B2

## (12) United States Patent

## Konda

## (10) Patent No.:

US 8,269,523 B2

## (45) **Date of Patent:**

## Sep. 18, 2012

## (54) VLSI LAYOUTS OF FULLY CONNECTED GENERALIZED NETWORKS

(75) Inventor: Venkat Konda, San Jose, CA (US)

(73) Assignee: Konda Technologies Inc., San Jose, CA

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 183 days.

(21) Appl. No.: 12/601,275

(22) PCT Filed: May 22, 2008

(86) PCT No.: PCT/US2008/064605

§ 371 (c)(1),

(2), (4) Date: May 31, 2010

(87) PCT Pub. No.: WO2008/147928

PCT Pub. Date: Dec. 4, 2008

### (65) **Prior Publication Data**

US 2011/0037498 A1 Feb. 17, 2011

## Related U.S. Application Data

- (60) Provisional application No. 60/940,394, filed on May 25, 2007.

- (51) **Int. Cl. H03K 19/177** (2006.01)

## (56) References Cited

## U.S. PATENT DOCUMENTS

| 4,813,038 | A | * | 3/1989 | Lee           | 370/390 |

|-----------|---|---|--------|---------------|---------|

| 5,406,556 | A | * | 4/1995 | Widjaja et al | 370/381 |

| 5,856,977 A * 6,049,542 A * 6,157,643 A * 6,567,858 B1 * 6,940,308 B2 * 7,136,380 B2 * 7,154,887 B2 * | 4/2000<br>12/2000<br>5/2003<br>9/2005<br>10/2006<br>11/2006<br>12/2006 | Yang et al. 370/395.72   Prasad 370/386   Ma 370/389   Yang et al. 709/238   Wong 326/41   Sailor 709/238   Li 370/388   Wu et al. 370/388 |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7,154,887 B2 * 7,346,049 B2 * 7,349,387 B2 *                                                          | 3/2008                                                                 | Wu et al.   370/388     Towles   370/386     Wu   370/360                                                                                  |  |  |  |  |  |

| (Continued)                                                                                           |                                                                        |                                                                                                                                            |  |  |  |  |  |

Primary Examiner — Vibol Tan

#### (57) ABSTRACT

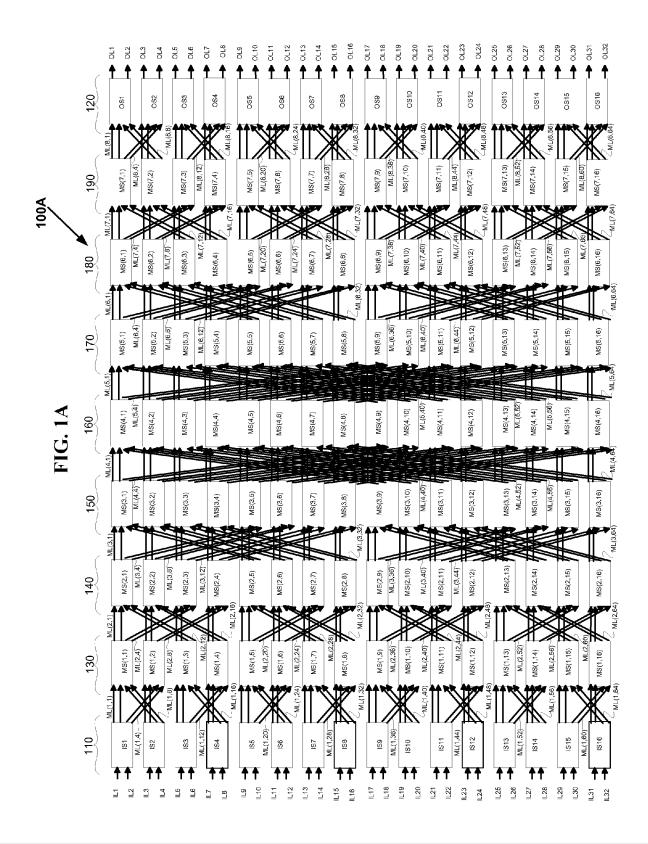

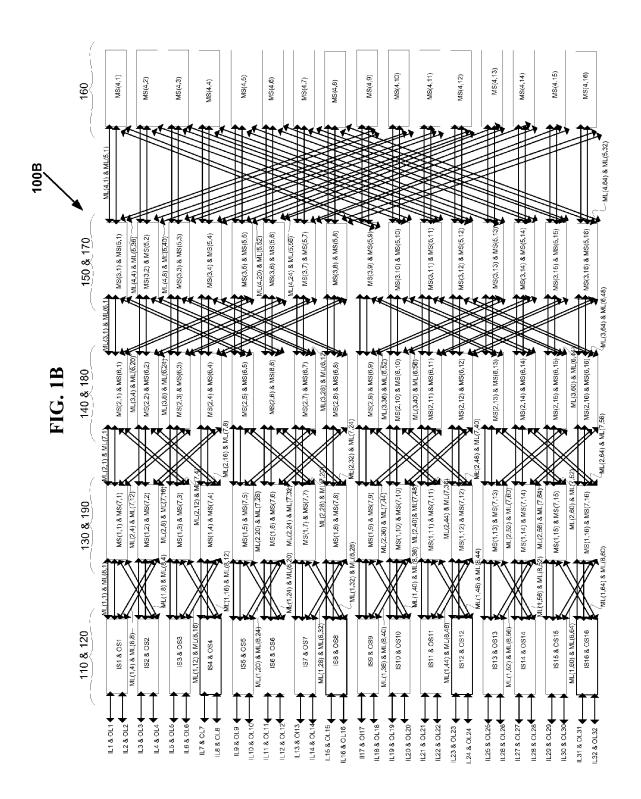

In accordance with the invention, VLSI layouts of generalized multi-stage networks for broadcast, unicast and multicast connections are presented using only horizontal and vertical links. The VLSI layouts employ shuffle exchange links where outlet links of cross links from switches in a stage in one sub-integrated circuit block are connected to inlet links of switches in the succeeding stage in another sub-integrated circuit block so that said cross links are either vertical links or horizontal and vice versa. In one embodiment the sub-integrated circuit blocks are arranged in a hypercube arrangement in a two-dimensional plane. The VLSI layouts exploit the benefits of significantly lower cross points, lower signal latency, lower power and full connectivity with significantly fast compilation.

The VLSI layouts presented are applicable to generalized multi-stage networks  $V(N_1, N_2, d, s)$ , generalized folded multi-stage networks  $V_{fold}(N_1, N_2, d, s)$ , generalized butterfly fat tree networks  $V_{hfl}(N_1, N_2, d, s)$ , generalized multi-link multi-stage networks  $V_{mlimk}(N_1, N_2, d, s)$ , generalized folded multi-link multi-stage networks  $V_{fold-mlimk}(N_1, N_2, d, s)$ , generalized multi-link butterfly fat tree networks  $V_{mlimk-bfl}(N_1, N_2, d, s)$ , and generalized hypercube networks  $V_{hcube}(N_1, N_2, d, s)$ , for s=1, 2, 3 or any number in general. The embodiments of VLSI layouts are useful in wide target applications such as FPGAs, CPLDs, pSoCs, ASIC placement and route tools, networking applications, parallel & distributed computing, and reconfigurable computing.

## 48 Claims, 39 Drawing Sheets

## **US 8,269,523 B2**Page 2

| U.S. PATENT DOCUMENTS               | , ,                 | Carr et al 370/388 |

|-------------------------------------|---------------------|--------------------|

| 7,397,796 B1 * 7/2008 Smiljani      |                     | Feng et al         |

| 7,424,011 B2 * 9/2008 Konda 370/388 | * cited by examiner |                    |

U.S. Patent

Sep. 18, 2012

Sheet 1 of 39

US 8,269,523 B2

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

## API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

## **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

## **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

## **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.